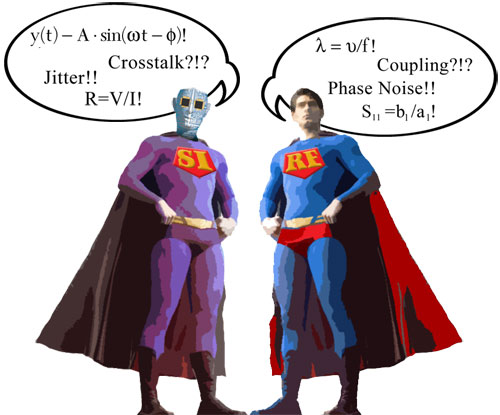

Fans of the television show “Seinfeld” likely remember the “Bizarro Jerry” episode in which Elaine befriended three guys, each of whom were polar opposites to Jerry, George and Kramer. The bizarro theme was borrowed from an old “Superman” plotline, satirizing characters who were very similar and yet very different from the show’s regulars. In the technical world, the bizarro counterpart to an RF/microwave engineer might be the signal integrity (SI) engineer. Consider the following. They work with data in the 1/frequency (aka time) domain, they work to suppress circuit radiation, they refer to coupling as cross-talk and they have a large annual conference/exhibition, aka DesignCon, which takes place this year from January 30th through February 2nd at the Santa Clara Convention Center.

Fans of the television show “Seinfeld” likely remember the “Bizarro Jerry” episode in which Elaine befriended three guys, each of whom were polar opposites to Jerry, George and Kramer. The bizarro theme was borrowed from an old “Superman” plotline, satirizing characters who were very similar and yet very different from the show’s regulars. In the technical world, the bizarro counterpart to an RF/microwave engineer might be the signal integrity (SI) engineer. Consider the following. They work with data in the 1/frequency (aka time) domain, they work to suppress circuit radiation, they refer to coupling as cross-talk and they have a large annual conference/exhibition, aka DesignCon, which takes place this year from January 30th through February 2nd at the Santa Clara Convention Center.

SI engineers work with digital signals commonly operating at multi-gigabit data rates, over ever-increasing distances and through a wide variety of mediums. They are responsible for analyzing and mitigating the effects that degrade the fidelity of the signal path, from internal connections of the integrated circuit (IC), through the package, the printed circuit board (PCB), the backplane, and any inter-system connections. Where the RF engineer is concerned with harmonics, intermodulation distortion, insertion loss, mismatch and noise figure, the SI engineer is concerned with ringing, ground bounce, distortion, signal loss, and power supply noise. While much of the terminology between RF and SI engineers are different, the physics of high speed signal transmission remains the same and so it is no surprise that many well known companies in the microwave industry participate in DesignCon every year.

In particular, DesignCon attracts the leading RF test and measurement equipment manufacturers, including Agilent Technologies, Anritsu,

LeCroy, National Instruments, Noisecom, Rohde & Schwarz and Tektronix; EDA and EM simulation vendors, such as Agilent EEsof, Applied Simulation Technology, ANSYS, AWR, Cadence, CST, Intercept Technology, Mentor Graphics, Synopsys, and Sonnet Software; as well as component and material manufacturers, such as ARC Technologies, Hittite Microwave, Huber + Suhner, Molex, Samtec, Rosenberger and Rogers Corp. The presence of these companies at DesignCon says a lot about the similar technical challenges faced by the microwave engineer and his SI counterpart. The engineering still comes down to design entry, characterizing the signal path (EM simulation), modeling the active devices, circuit/system simulation and optimization, fabrication and test.

And yet, these companies market familiar products in a slightly altered language at DesignCon. For instance, last year Agilent promoted the use of its ADS Momentum for solving power integrity problems on PCBs “complicated by heavily perforated power and ground planes.” In SI and PI analysis, engineers characterize the signal path or interconnect channel using many of the same EM simulation tools used by the microwave community. For the microwave engineer, EM simulation tools provide the interconnecting transmission line or component’s defining S-parameters and the designer is good to go. But for the SI engineer, interest lies in what happens to the data waveform as it passes through the signal path rather than the frequency behavior of the path itself. And so the SI engineer needs a model for the transmission channel that works in the time domain as well as representation of the waveform and all of the I/Os that will impact the waveform in the network under analysis. Rather than use RF compact or behavioral models, EDA products targeting DesignCon attendees such as Agilent’s ADS, AWR’s Microwave Office or ANSYS’ SI Designer feature input/output buffer information specification algorithmic modeling application programming interface (IBIS AMI) standard. This standard allows IC vendors to share “executable datasheets” of the high speed digital SERDES without proprietary encryption.

One of the on going challenges from a simulation perspective has been the use of S-parameter networks in signal integrity time domain analyses. The signal integrity analysis of high speed electronic designs requires that the interconnect models be valid over a wide bandwidth. Due to simulation or measurement errors, the S-parameters of interconnect structures can become non-passive. Although a number of simulators can perform transient simulation directly with S-parameters, they will often experience convergence problems if the measured or simulated data violates passivity. Perhaps for this reason, conference organizers are offering a special session on “How to Avoid Butchering S-parameters.” Several software vendors address the issue with tools that provide data integrity checks, allowing users to verify and enforce the passivity, reciprocity and causality of S-parameters.

The Conference Program

Like the International Microwave Symposium, the technical program committee (TPC) consists of volunteers who conduct a peer review of submitted abstracts and papers. Unlike IMS, these reviewers are not members of a technical society, such as the MTT-S, but rather individuals from a broad collection of companies and universities that represent organizations at the forefront of the high speed electronics industry. This year’s TPC is comprised of individuals from Cadence, IBM, Intel, Sigrity, Dell, Tektronix, the Mayo Clinic, Xilinx, nVidia, Apple, CST, Infineon and Cisco, to name just a few. The 2012 TPC consists of 146 reviewers from all areas of the high speed design spectrum.

The conference includes a number of sessions that will make an RF/microwave engineer feel right at home, including one on RF/Microwave Techniques for Signal Integrity. With a focus on the complete signal path, the conference organizers have the challenge of presenting a technical program that spans many mediums and several disciplines – from design, simulation, verification and test. This is reflected in the different design tracks available to attendees, including analog and mixed-signal design and verification, EMC/EMI, FPGA design and debug, high speed serial design, processing, equalization and coding, power integrity and power distribution network design as well as memory and parallel interface design. To address the challenges of designing high speed channels in different mediums, there will be sessions on chip-level design for signal/power integrity, PCB design tools and methodologies and a track on system co-design: chip/package/board. On the simulation, analysis and test side, there will be tracks on high speed timing, jitter and noise analysis, PCB materials, processing and characterization, and test and measurement methodology.

![]() As signaling rates increase into the multi-gigabit-per-second range, SI engineers are forced to confront the phenomena that impacts circuit behavior at higher frequencies. Our SI counterparts will increasingly need the expertise and knowledge base of RF and microwave engineers to extend the range of the signal integrity toolkit. To participate in this exchange of knowledge or experience the SI world of our bizarro brethren firsthand, RF/microwave companies and engineers should make the journey to DesignCon 2012. As an SI engineer might say, “it is sure to be eye opening.”

As signaling rates increase into the multi-gigabit-per-second range, SI engineers are forced to confront the phenomena that impacts circuit behavior at higher frequencies. Our SI counterparts will increasingly need the expertise and knowledge base of RF and microwave engineers to extend the range of the signal integrity toolkit. To participate in this exchange of knowledge or experience the SI world of our bizarro brethren firsthand, RF/microwave companies and engineers should make the journey to DesignCon 2012. As an SI engineer might say, “it is sure to be eye opening.”

Chiphead image courtesy of DesignCon.

Superman and Bizarro images courtesy of DC Comics.