We paid our annual homage to the coolest event mascot, Chiphead, at DesignCon 2017. DesignCon is the annual meeting place for chip, board, and systems design engineers taking place at the end of January each year in Santa Clara, CA. The event serves the high speed communications and semiconductor communities offering state-of-the-art design methodologies, applications and technologies. The event was relatively busy this year and the exhibition participation was strong. There were more than 100 sessions spanning 14 tracks covering all aspects of electronic design; from chips through boards and systems.

Heidi Barnes of Keysight Technologies was selected as the recipient of the 2017 Engineer of the Year Award at the event. She was selected for her dedication to problem solving and enthusiasm for leading and collaborating with teams as a leader in the industry.

Heidi Barnes of Keysight Technologies was selected as the recipient of the 2017 Engineer of the Year Award at the event. She was selected for her dedication to problem solving and enthusiasm for leading and collaborating with teams as a leader in the industry.

The Signal Integrity Journal and Microwave Journal editors were covering the latest product and technology innovations on the exhibition floor. Here is a summary (video demos can be found HERE):

Test/Measurement

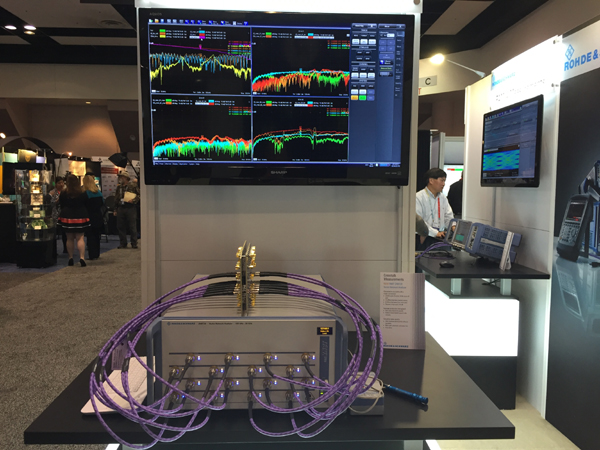

Rohde & Schwarz added a new 6 GHz model to its R&S RTO2000 series, opening up measurements on fast communications interfaces and IoT applications. The new scope with 6 GHz bandwidth allows developers to test the radio interfaces of 802.11ac WLAN components for IoT modules in the 5 GHz band as well as fast communications interfaces such as USB 3.1 Gen 1 with data rates of 5 Gbit/s. With its multi-domain functionality, only a single compact instrument is needed to analyze power supplies, processors and sensors with up to 6 GHz bandwidth. Synchronized time, frequency, protocol and logic analyses results allow users to debug at the system level. It offers users the best oscilloscope performance in its class with up to 16-bit vertical resolution in high definition mode and offers one million waveforms per second. Rohde & Schwarz also expanded the functionality of its R&S RTE and R&S RTO digital oscilloscopes to include a triggering and decoding option for the new CXPI protocol.

Rohde & Schwarz added a new 6 GHz model to its R&S RTO2000 series, opening up measurements on fast communications interfaces and IoT applications. The new scope with 6 GHz bandwidth allows developers to test the radio interfaces of 802.11ac WLAN components for IoT modules in the 5 GHz band as well as fast communications interfaces such as USB 3.1 Gen 1 with data rates of 5 Gbit/s. With its multi-domain functionality, only a single compact instrument is needed to analyze power supplies, processors and sensors with up to 6 GHz bandwidth. Synchronized time, frequency, protocol and logic analyses results allow users to debug at the system level. It offers users the best oscilloscope performance in its class with up to 16-bit vertical resolution in high definition mode and offers one million waveforms per second. Rohde & Schwarz also expanded the functionality of its R&S RTE and R&S RTO digital oscilloscopes to include a triggering and decoding option for the new CXPI protocol.

R&S introduced the RT-ZPR20, a new, low-noise power rail probe with a bandwidth of 2 GHz. Its 1:1 attenuation also ensures very good sensitivity. The large offset range of ± 60 V permits analysis of the smallest disturbance signals during power integrity measurements, even on DC power supplies with a high voltage level. The probe also features an integrated high-precision DC voltmeter. They also introduced the RT-ZP1X passive 1:1 probe that broadens the application range of its R&S RTO and R&S RTE series oscilloscopes. Both the probe and the oscilloscopes' frontend are extremely low noise, making this combination ideal for measuring the smallest of signals down to 1 mV/div, e.g. for power integrity measurements on integrated circuits and components.

The R&S Scope Rider now combines the functionality of eight instruments. New features include a spectrum analyzer, a frequency counter and a harmonic analyzer for evaluating the quality of power supplies. The right tool is always available, both in the lab and when on the road performing installation, service and maintenance activities. Since the fully insulated, handheld instrument meets measurement category CAT IV requirements, it can be used to perform measurements at the source of low-voltage installations up to 600 V.

Anritsu Company demonstrated signal integrity solutions featuring their Signal Quality Analyzer (SQA) MP1800A BERT, as well as the VectorStar® and ShockLine™ vector network analyzers (VNAs). Among the demonstrations was a 56G/112 NRZ and PAM4 accurate jitter tolerance test system featuring the MP1800A with the G0374A 64 Gbaud PAM4 DAC and MP1825B 4-tap emphasis that satisfies the high accuracy and margin requirements of communications standards such as OIF, IEEE, and InfiniBand. For high-speed serial bus verification, the MP1800A was integrated with the MP1825B and Vector Signal Generator MG3710A to conduct jitter tolerance tests on PCIe and 100GE interfaces.

Anritsu Company demonstrated signal integrity solutions featuring their Signal Quality Analyzer (SQA) MP1800A BERT, as well as the VectorStar® and ShockLine™ vector network analyzers (VNAs). Among the demonstrations was a 56G/112 NRZ and PAM4 accurate jitter tolerance test system featuring the MP1800A with the G0374A 64 Gbaud PAM4 DAC and MP1825B 4-tap emphasis that satisfies the high accuracy and margin requirements of communications standards such as OIF, IEEE, and InfiniBand. For high-speed serial bus verification, the MP1800A was integrated with the MP1825B and Vector Signal Generator MG3710A to conduct jitter tolerance tests on PCIe and 100GE interfaces.

The MP1800A was also be configured with the ShockLine Economy Vector Network Analyzer (VNA) MS46524B, along with Granite River Labs calibration and receiver test software to create an automated, simple, and efficient method to test Thunderbolt 3 Receiver CTS. To support the latest USB3.1 Gen2 SuperSpeed+, 10 Gbit/s receiver test standards, Anritsu showed the MP1800A with its new USB3.1 Receiver Test Adapter G0373A and dedicated high-speed serial data test software. Also in the Anritsu booth was the VectorStar VNA series in multiple configurations. One station will include a 70 GHz 4-port signal integrity solution and another will be a 4-port 70 kHz-110 GHz broadband VNA solution for on-wafer device characterization.

Keysight Technologies demonstrated a wide variety of high-speed digital solutions including:

- USB 3.1/Type-C Tx/Rx/PD Test — The latest USB Type-C transmitter and receiver test solutions, developed to properly characterize and validate USB designs, as well as its cable and connector test solution using its network analyzer with the TDR option.

- PCIe® Rx/Tx Test —Tools and techniques that engineers can use to test PCI Express 4.0 devices, specifically the physical layer Gen4 requirements for transmitters and receivers.

- Signal Integrity and Power Integrity — A cohesive solution for signal and power integrity analysis. This includes new design and test techniques to gain rapid insight, as well as new channel simulation techniques. Keysight's Physical Layer Test System (PLTS) 2017 is a new software release and features PAM-4 eye diagrams, channel operating margin (COM) and a SCPI command interface for manufacturing automation applications. Keysight demonstrated its new Digital Interconnect Test System Reference Solution, used to enable signal integrity characterization of multiport interconnect products.

- 400G/PAM-4 — New measurement techniques, including its new M8040A highly integrated 64 Gbaud high-performance BERT, developed for testing electrical and optical PAM-4 transmitters and receivers.

- Data Analytics — New data analytics software capability that addresses the need for data management and efficient and intuitive measurement analysis.

- DDR4/DDR5 Memory Test and Validation — Keysight demonstrated how to easily acquire cross-correlated measurements of traffic on DDR/LPDDR buses and the power integrity of systems, as well as innovative new probing and debug techniques that provide rapid insights for engineers into their high-speed memory systems.

- Flexible Multi-Level Signal Generation — Using its M8195A and M8196A AWGs, Keysight will demonstrated how to generate multi-level signals, such as HDMI, MIPI, and PAM-16 802.3bz.

National Instruments introduced the VB-8054, a new higher performance model of VirtualBench. VirtualBench plays a key role in reducing the cost and footprint of test and measurement systems by consolidating five of the most commonly used instruments into one device without compromising the performance of each instrument. Combined with a modern software experience and simple programming interface, VirtualBench creates new efficiencies for engineers interacting with benchtop test equipment or developing low-cost automated test systems. The VirtualBench hardware family consists of three models most easily designated by oscilloscope analog bandwidth: 100, 350 and 500 MHz. Through these models, the VirtualBench family serves a wide range of applications and price points in academic labs, hardware characterization/debug benches and automated test systems.

Teledyne LeCroy exhibits included the HDO family of 12-bit high definition oscilloscopes; PAM4 signal analysis; digital power management IC, power sequencing, and power-integrity testing; USB 3.1 and Power Delivery compliance test over Type-C; MIPI M-PHY physical- and protocol-layer test; PCI Express Tx/Rx compliance; DDR compliance and debug capabilities; and the first SAS 4.0 Analyzer Platform.

Teledyne LeCroy exhibits included the HDO family of 12-bit high definition oscilloscopes; PAM4 signal analysis; digital power management IC, power sequencing, and power-integrity testing; USB 3.1 and Power Delivery compliance test over Type-C; MIPI M-PHY physical- and protocol-layer test; PCI Express Tx/Rx compliance; DDR compliance and debug capabilities; and the first SAS 4.0 Analyzer Platform.

The next evolution of the enterprise storage standard, SAS 4.0 doubles the effective bandwidth over the current 12Gb/s SAS specification yet preserves backward compatibility to enable easier data center adoption. The Teledyne LeCroy exhibit featured the Sierra T244 Protocol Analyzer platform, the first commercially available solution for testing and validating SAS 4.0 protocol. They also announced the addition of fully automated transmitter testing for 56-Gb/s, PAM4-based interfaces. The new QPHY-56G-PAM4 option adds standards-specific measurement capabilities to a measurement portfolio that already includes the PAM4 signal analysis capabilities pioneered by Teledyne LeCroy in recent years.

Noisecom (WTG) had their J9000 Jitter Generator Demonstration going in the booth that emulates additive white Gaussian noise (AWGN) channel on a 10GBase signal by adding analog broadband (5 GHz) AWGN on differential data lines using J9010. In the demo set up, the SHF bit pattern generator outputs 10 GHz clocked data into the J9010. J9010 injects controlled AWGN to the data lines to emulate AWGN channel. As the amount of AWGN increases the impact on the eye diagram can be observed on the LeCroy WaveMaster. Total jitter is measured and eye diagram is monitored. This is a low cost setup compared to other methods. The J7000 and custom J9000series generate “real world” random jitter, commonly referred to as Rj in the Stochastic Total Jitter model, by introducing AWGN with a large crest factor in 0.1 dB steps to the differential data lines. The combined signal output can then be measured using an oscilloscope, BERT, or Time Interval Analyzer (TIA).Unlike BERT and bit pattern generators where jitter is introduced by jittering the clock timing, J9000 series emulates the AWGN channel by adding analog noise on to the channel. This simulates the effect of noise coupled on to the signal in real life transmission environments for receiver sensitivity testing and cross talk dictated by IEEE 802.3 standards.

Software

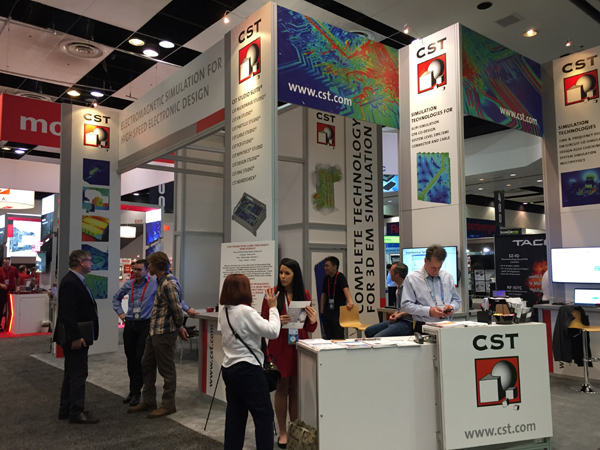

CST was showing off EMC STUDIO® (CST EMCS) which is a specialized software package for analyzing EMC/EMI using 3D electromagnetic field simulation. The solvers and tools in CST EMCS have been selected to be especially relevant to EMC engineers, and are drawn from the mature technology of CST STUDIO SUITE® and CST BOARDCHECK®. The range of solvers allow emissions and susceptibility to be investigated across a range of different components. Alongside the general purpose time and frequency domain solvers, CST EMCS also includes cable harness solvers, EDA and CAD import tools, circuit simulation tools, PCB design rule checking and compact models for simulating vents and seams efficiently. With CST's System Assembly and Modeling (SAM) framework, simulations of individual components can also be combined for a hybrid simulation. Through its dedicated EMC workflows, CST EMCS can be integrated into a wide range of product design processes. They also recently released CST Studio 2017 that includes new features such as both front-end and back-end improvements across the suite, with many focusing on tools for synthesizing and simulating componentsas well as for managing and analyzing these components as systems.

CST was showing off EMC STUDIO® (CST EMCS) which is a specialized software package for analyzing EMC/EMI using 3D electromagnetic field simulation. The solvers and tools in CST EMCS have been selected to be especially relevant to EMC engineers, and are drawn from the mature technology of CST STUDIO SUITE® and CST BOARDCHECK®. The range of solvers allow emissions and susceptibility to be investigated across a range of different components. Alongside the general purpose time and frequency domain solvers, CST EMCS also includes cable harness solvers, EDA and CAD import tools, circuit simulation tools, PCB design rule checking and compact models for simulating vents and seams efficiently. With CST's System Assembly and Modeling (SAM) framework, simulations of individual components can also be combined for a hybrid simulation. Through its dedicated EMC workflows, CST EMCS can be integrated into a wide range of product design processes. They also recently released CST Studio 2017 that includes new features such as both front-end and back-end improvements across the suite, with many focusing on tools for synthesizing and simulating componentsas well as for managing and analyzing these components as systems.

Cadence enables global electronic design innovation and plays an essential role in the creation of today's integrated circuits and electronics. They had several demos including:

•Constraint-driven power integrity design and analysis featuring easy setup with automated model and source/sink assignments

•Power-aware simulation and rule checks for DDR4 memory interface design and analysis

•Multi-gigabit serial link design and analysis featuring compliance testing for popular interfaces such as PCIe 4.0

•Streamlining the flow between IC design and package/PCB design

•PCIe 4.0 controller and PHY bring-up and interoperability

Mentor Graphics showcased their tools including:

•HyperLynx Signal Integrity

•HyperLynx Power Integrity

•HyperLynx DRC

•HyperLynx Full-Wave Solver

•Frontline InStack Design

Ataitec was featuring ADK which is a comprehensive set of SI utility tools to simplify many commonly encountered SI tasks to a single mouse click. ADK has been used daily for many years in major hardware companies. With ADK, new graduates can be trained to perform the tasks of middle-level SI engineers within a day. Among the 25+ SI Apps are

•Fill in DC and correct passivity, reciprocity and causality errors in Touchstone files,

•Convert S parameters into TDR/TDT waveforms,

•Compute optimized TX tap coefficients, run channel simulation and plot eye diagrams,

•Convert S parameters into equivalent SPICE models,

•Combine multiple .snp files,

•Compliance testing, 2D field solver, S-param viewer and more.

ANSYS’ automated design flow can perform transient circuit simulation of ECAD and MCAD assemblies directly from a layout for full system verification. Their software maximizes the power efficiency of devices and accurately predicts important electrothermal behavior and electromagnetic coupling within compact designs. ANSYS solves highly complex electronic assemblies and automatically produces transient plots for TDR, eye diagrams and compliance reports. This first-in-the-industry design flow can perform DC analysis, map Joule heating to a mechanical solver, and then produce temperature profiles and associated mechanical deformation and stress maps. It’s a chip-package-system solution that allows you to evaluate electrical, thermal and structural behavior, so your design team can optimize system performance prior to building and testing. Dr. Zoltan Cendes, founder of Ansoft (acquired by ANSYS in 2008), delivered the keynote speech sharing his insights on how signal integrity simulation has been turned inside out with electromagnetic field simulation.

Cables and Connectors

Samtec displayed their high-speed technologies for Silicon-to-Silicon system optimization, including a product demonstration of PCIe® Gen 3 fabric enabled by our FireFly™ mid-board technology, Flyover QSFP28 cable assembly, ExaMAX® high-speed backplane and Edge Rate® HD multi-row interconnects. Samtec’s Silicon-to-Silicon system optimization provides engineers the service, products, tools and resources to optimize the entire signal path from bare die to IC package and assembly to PCB to connectors and cable assemblies and back again. Learn more about Silicon-to-Silicon system optimization.

Samtec displayed their high-speed technologies for Silicon-to-Silicon system optimization, including a product demonstration of PCIe® Gen 3 fabric enabled by our FireFly™ mid-board technology, Flyover QSFP28 cable assembly, ExaMAX® high-speed backplane and Edge Rate® HD multi-row interconnects. Samtec’s Silicon-to-Silicon system optimization provides engineers the service, products, tools and resources to optimize the entire signal path from bare die to IC package and assembly to PCB to connectors and cable assemblies and back again. Learn more about Silicon-to-Silicon system optimization.

Their flyover QSFP28 cable assembly (FQSFP Series) achieves 28 Gbps performance and is backward compatible with all QSFP assemblies. This direct attach system, with press-fit tails that provide low speed signals and power to the PCB, allows drivers to be remotely located for design flexibility and greater control over thermal cooling. Signal integrity is optimized by flying critical data over lossy PCB via Samtec’s ultra-low skew pair twinax cable with inherently lower attenuation. Re-timers are not required reducing cost and power consumption.

The ExaMAX® high-speed backplane system (EBTM/EBTF-RA Series) enables 28 Gbps performance on a 2.00 mm column pitch with a roadmap to 56 Gbps. This rugged system has the industry’s lowest mating force with excellent normal force, a 2.4 mm contact wipe and two points of contact for high reliability. Among other industry specifications, ExaMAX® exceeds OIF CEI-28G-LR for 28 Gbps standards and meets the Telcordia GR-1217 CORE specification. The roadmap for ExaMAX® products includes cable, direct mate orthogonal, mid-plane orthogonal and coplanar.

Edge Rate® HD, Samtec’s new 0.635 mm pitch, high-speed, multi-row strip – packages the same reliable contact system and ease of processing found in the SEARAY™ family in an even smaller and higher-density strip design. With both the four-row (5 mm wide) and two-row (2.5 mm wide; in development) versions capable of supporting 28+ Gbps applications, as well as multiple next-generation protocols.

Samtec’s x4 duplex 28 Gbps FireFly™ optical engine (ECUO Series) brings its industry-leading density to the 100 Gbps Datacom/Telecom and HPC markets. Designed with thermal optimization in mind, options are available for both forced air and cold plate cooling scenarios. The integral dual-band CDR was designed to work with the latest Ethernet and InfiniBand™ protocol specifications. This x4 duplex architecture, while offering an extremely small footprint on the board, makes FireFly™ ideal for communications within a rack, or between racks.

Huber+Suhner was featuring SUCOFLEX 526V which is the only VNA microwave cable assembly with max. 50 ppm phase variation vs. temperature between +15 °C and +30 °C. It shows no “PTFE phase knee” at +19°C as on conventional VNA test cable assemblies which cause phase variations and unstable measurements in critical laboratory conditions. SUCOFLEX 526V is available in three standard lengths with ruggedized 3.5 mm VNA-style connectors.

Rosenberger displayed a new technology to improve signal integrity with true coaxial connectivity on µm scale with it unique Coax Wire Bond technology. Based on process steps commonly used in semiconductor manufacturing, wire bonds are transferred into impedance controlled coaxial connections with a typical outer diameter of 70 µm. This enables new leading edge solutions for demanding RF applications by improving bandwidth, while reducing crosstalk and EMI. The coaxial connection can be attached directly onto semiconductor dies and various lead frame / substrate materials.

Rosenberger displayed a new technology to improve signal integrity with true coaxial connectivity on µm scale with it unique Coax Wire Bond technology. Based on process steps commonly used in semiconductor manufacturing, wire bonds are transferred into impedance controlled coaxial connections with a typical outer diameter of 70 µm. This enables new leading edge solutions for demanding RF applications by improving bandwidth, while reducing crosstalk and EMI. The coaxial connection can be attached directly onto semiconductor dies and various lead frame / substrate materials.

Carlisle Interconnect Technologies' AltaVel family of open pin field High Speed Digital (>25 Gbps) Interconnect was featured as it is optimized to provide scalability and reliability in dense, high mate/de-mate cycles applications. The broad family of connectors are available in Board to Board, Board to Cable, Cable to Cable and Cable to Panel configurations. All configurations are available in the following styles; Vertical to Vertical, Right Angle to Vertical and Right Angle to Right Angle. These standard connectors are part of CarlisleIT's full lineup of cost effective, off the shelf and customizable interconnect solutions. This product will be available 3Q 2017.

TE Connectivity was showing off broad range of products including the STRADA Whisper product family operates with extremely low noise, low insertion loss and little to no skew—all of which provide system architects with design flexibility and high design margin. Specific versions are available for 100-Ohm and 85-Ohm applications so there is no need to compromise on impedance discontinuities. Mechanically, the STRADA Whisper connector family mirrors most high-speed backplane connectors in the market for easy implementation. It differentiates itself through folded signal pins surrounded by strong, protective C-shaped shields, which make the product family one of the most robust offerings in the market. Additionally, the connector footprint keeps crosstalk down and the overall connector design uses latest eye-of-needle technology.

Molex introduced the Impulse™ Orthogonal Direct Backplane Connector System. Designed for high-density data center applications, the new Impulse connector system supports data rates of 56 Gbps NRZ and 112 Gbps PAM4 with superior signal integrity. The 2.00mm column-to-column pitch of the Impulse system delivers high-speed connectivity in a compact size. The innovative signal interface improves insertion loss over traditional in-line interface, pushing resonance beyond 35 GHz.