The point where wireless communication and ubiquitous connectivity became an essential part of our lives has already passed. Generation after generation, communication speed is being taken to unprecedented levels, requiring both state-of-the-art hardware and software to handle a huge volume of data, delivered to an increasing number of users in an overcrowded spectrum. As tough as it sounds, to our delight the challenges are always plentiful.

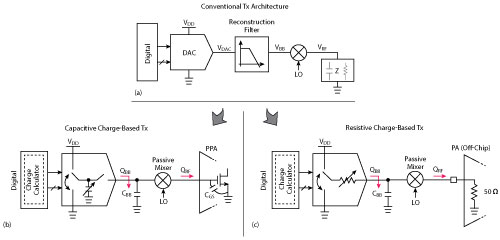

Figure 1 Conventional Tx architecture (a) with capacitive10 (b) and resistive11 (c) charge-based realizations.

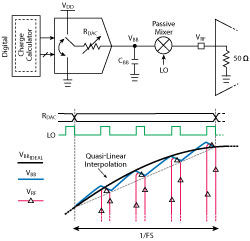

Figure 2 Quasi-linear interpolation improves alias attenuation.

With respect to the radio front-end, providing extremely low noise emission with improved signal integrity are key requirements to supporting high-order modulation schemes (e.g., 64 QAM) in situations where anyone’s transmitter can be interfering with a neighboring user or its own receiver in frequency-division full duplex. On the transmit side, linearity requirements are commonly translated into ACLR and EVM parameters, whereas out-of-band noise is typically defined by the maximum power spectral density allowed in the receive band. Increasing power consumption or area are not options. On the contrary, for an improved user experience, the battery should last longer, and the price per component should always go down so that more and more features can be added to the mobile device. Thus, making a better performing radio front-end that consumes even less power and is smaller is a hot research topic, especially the transmitter and power amplifier (PA) designs — considered by many the “battery killers” on most mobile devices.

ANALOG vs. DIGITAL-INTENSIVE

A quick analysis of literature shows that the state-of-the-art for transmitter implementations is divided into analog and digital-intensive architectures. In terms of out-of-band noise, analog intensive architectures are undoubtedly the best performing implementations.1–5 However, their improved noise performance is typically achieved through extensive lowpass filtering along the entire signal path, which has a significant impact in area consumption. To filter out quantization noise and the sampling aliases from the digital-to-analog conversion, bulky reconstruction filters (which can use up to 1.37 mm2) are commonly used.3 The implementation of such analog blocks is becoming more and more difficult using digital-driven, highly-scaled CMOS technologies. The reduced supply voltage, limited transistor gain and increased leakage are a few of the issues aggravated with every new technology node.

Digital-intensive implementations, on the other hand, are by far the most portable, area efficient and scaling friendly.6–9 However, the lack of filtering for both noise and aliases makes it very challenging to meet the stringent out-of-band noise requirements with a SAW-less design. The direct digital-to-RF conversion leaves no analog path for a reconstruction filter to be introduced, so both quantization noise and sampling aliases are up-converted to RF frequencies without any attenuation. In these architectures, the quantization noise is addressed by either increasing the number of bits in the digital-to-analog converter (DAC), Σ∆ modulation or filters notching at specific parts of the spectrum (e.g., the receive band in frequency division duplex (FDD) systems). The aliases, in turn, are often attenuated by the sinc transfer function, using large sampling frequencies. Nevertheless, depending on the overhead circuitry and speed, some of these solutions conflict with the intended reduction in power consumption and area.

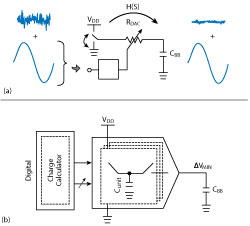

Figure 3 Noise filtering mechanisms: the signal-dependent RC filter attenuates uncorrelated noise (a) and the charge-based architecture reduces quantization noise (b).

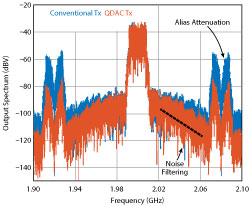

Figure 4 Output spectrum showing both noise and alias reduction provided by the charge-based architecture.

INCREMENTAL CHARGE-BASED OPERATION

A novel, digital-intensive transmitter architecture that can relax this trade-off was first presented at ISSCC 2015.10 Through the combination of charge-domain operation with incremental signaling, this architecture gives the best of both worlds, providing the reduced area and high portability of digital-intensive architectures and the improved out-of-band noise performance from intrinsic noise filtering capabilities.

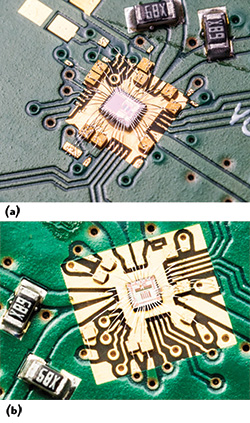

Figure 5 Capacitive (a) and resistive (b) charge-based Tx prototypes. With the resistive prototype, an out-of-band noise spectral density of –159 dBc/Hz was achieved at 45 MHz offset, using an area of only 0.22 mm².

The simple observation of a conventional transmitter implementation leads to the conclusion that the modulator is always driving a capacitive load, either an active mixer input transistor or the pre-power amplifier (PPA) input capacitance driven through a passive mixer. In either case, providing the required speed and linearity demands low output impedance circuitry that typically increases power consumption significantly, especially when the signal swing is increased to improve the signal-to-noise ratio (SNR). Driving capacitance can be much more efficient if operated incrementally, in the charge domain. When all capacitances across the signal path are known, changing their voltages can be done by simply adding or subtracting charge. If no biasing is required, the only charge taken from the supply corresponds to the increment — hence, the minimum charge needed to provide the desired voltage swings. The same reasoning applies even when the RF load is not capacitive.11

The operation of this architecture is based on two charge components, baseband (QBB) and RF (QRF). The baseband component represents the amount of charge required to drive a baseband capacitance CBB, moving the baseband voltage up and down as defined by the digital input signal. The RF charge, on the other hand, is the amount subtracted from CBB to drive the RF load every time the mixer switch is closed. As expected, the exact QRF depends on the nature of the RF load, whether resistive or capacitive (see Figure 1).10–11 Whenever a new baseband data sample arrives, a charge calculation block in the baseband processor determines how much extra charge should be accumulated on each one of the baseband capacitors and subsequently transferred to the RF output, so that every node follows its expected voltage excursion. The total amount of charge given by the sum of QBB and QRF (QTOTAL=QBB+ QRF) is then delivered from the supply to the baseband capacitors (and vice versa) by the so-called charge-based DACs (QDAC).

Two implementations of the incremental charge-based transmitter have been demonstrated since last year.10–11 They differ on how the QDAC is implemented and the RF load being driven. In the first, the RF load is the input capacitance of a PPA stage, and the QDAC is implemented with a controllable capacitance that is first pre-charged and then connected to CBB. Fractions of the total charge (QTOTAL) required per sampling period are conveyed at LO speed in discrete packets, sized by adjusting the DAC capacitance accordingly. In the second implementation, the ability of the charge-based architecture to deliver more power was investigated. Based on the observation that the first IC’s power consumption is highly impacted by the PPA bias current, a direct launch implementation was evaluated, where the PA is driven directly from the QDAC. In this case, the benefits include removing a power-hungry block from the signal path (i.e., the PPA) and increasing the effectiveness of pre-distortion by directly controlling the PA input — represented by a 50 Ω load in this implementation. In the direct launch case, the QDAC was implemented using a 12-bit conductance array, which proved to be the most area-efficient way of increasing the charge capacity of the QDAC. Instead of delivering packets of charge at the LO rate, as in the first implementation, the required total charge is transferred to the baseband node by charging and discharging CBB in continuous time. Since the DAC switches are operated at baseband speed (and not LO), further improvements in power consumption can also be achieved compared to the first implementation.

IMPROVED NOISE PERFORMANCE

Recapitulating, an important drawback of the RF DAC’s output spectrum is that baseband noise sources and spurs (including thermal noise, quantization noise and sampling aliases) are up-converted to RF without any filtering. However, the charge-based architecture can provide sensitive improvements in noise performance.

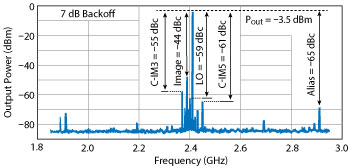

Figure 6 Measured output spectrum of resistive charge-based Tx, with 10 MHz single tone sampled at 500 MSPS.

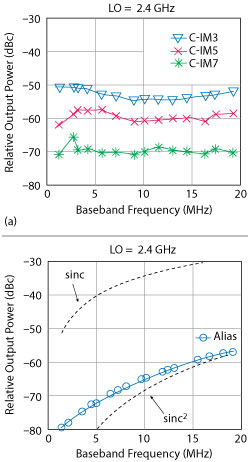

In transmitter architectures applying conventional DACs, the transmit signal is reconstructed from digital to analog at the baseband sampling rate. The resulting aliases are hence shaped by a sin(x)/x or sinc transfer function, inherent with zero-order hold systems. On the other hand, with the two charge-based architectures, without oversampling the digital input signal or increasing the interface speed of the QDAC, the continuous charge and discharge of CBB provides an inherent quasi-linear interpolation between the consecutive baseband samples (see Figure 2). The output spectrum in this case is shaped by a sinc2 transfer function that significantly attenuates the sampling aliases. For example, more than 20 dB of alias attenuation is inherently provided when a 20 MHz bandwidth signal is sampled at 500 MSPS.

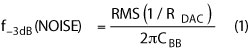

The intrinsic noise filtering capability of the architecture is another key enabler to improving the out-of-band noise performance. Clearly seen with the resistive QDAC implementation, the combination of the baseband capacitor CBB and the resistive QDAC array yields an inherent single-order lowpass filter in the signal path. However, since the resistive component is constantly changing over time, in order to adjust the amount of charge transferred to CBB, the cutoff frequency is not fixed. The equivalent RC time constant, which defines the filter cutoff frequency, is signal dependent, and automatically adjusted to provide the required instantaneous swing at the baseband node. As a result, the wanted signal is properly built at the baseband node without any attenuation. On the other hand, uncorrelated signals — not part of the digital input and which do not affect the charge calculations — do not have the same “on demand” bandwidth adjustment. Because of the architecture, they are filtered, with an equivalent cutoff frequency numerically approximated by the average QDAC conductance over time (see Figure 3a):12

This noise cutoff frequency, which applies to any noise contributor coupled to the baseband (including quantization), is a major advantage of the incremental charge-based transmitter.

Figure 7 Carrier to intermodulation power ratio (a) and relative alias power (b) vs. baseband frequency, with a 2.4 GHz LO.

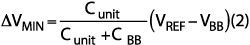

In addition to noise filtering, quantization noise is inherently improved by the charge-based architecture. Introduced whenever an infinite resolution analog signal is represented by its discretized digital counterpart, quantization noise for a given DAC is bounded by the minimum voltage or current step that can be created at its output. In a conventional architecture, it corresponds to the least significant bit (LSB), which is the full output scale divided by the total number of steps enabled by the number of bits. In a charge-based DAC, however, the minimum voltage step that can be resolved at the output is given by (see Figure 3b):

where VREF can be either VDD or ground (0 V), if the net charge in the system is being increased or decreased, respectively.

The ∆VMIN at the QDAC output is fundamentally determined by the ratio between Cunit and CBB and, as a result, the quantization noise on this charge-based transmitter can be decreased by simply choosing a small enough unit capacitance with respect to CBB, another remarkable feature of the proposed architecture. With a fixed 45 pF baseband capacitor, for example, a quantization noise SNR of 86 dB can be achieved with a 2 fF unit capacitance — roughly a 14-bit effective number of bits (ENOB). Both noise filtering and alias attenuation are obvious in Figure 4, which shows the simulated output spectrum of a 20 MHz baseband signal transmitted at 2 GHz.

MEASURED RESULTS

Both charge-based transmitter implementations were prototyped using 28 nm, 0.9 V CMOS technology (see Figure 5). The first charge-based transmitter consisted of a capacitive QDAC driving the PPA input through a 45 pF baseband capacitance. With a 10-bit DAC running at 128 MSPS, it demonstrates all the noise filtering capabilities of charge-based operation, notably a noise floor 15 dB lower than a transmitter using a conventional DAC with the same number of bits and operating at the same sampling frequency. At 45 MHz offset from a 1 GHz modulated carrier, it provides an out-of-band noise spectral density of -155 dBc/Hz and ACLR 1 and 2 of -42 dB and -47 dB, respectively.

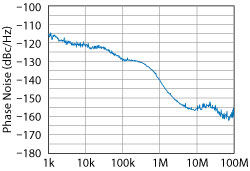

The same improved noise performance was achieved in the second implementation, where the PPA was removed from the signal path. In this case, the charge-based architecture demonstrated the ability to deliver considerable power by directly driving a 50 Ω load that represents the PA input. Two different external baluns were used to validate transmitter performance at both 900 MHz and 2.4 GHz. Achieving a peak power of 3.5 dBm with a 0.9 V supply, measurements with baseband frequencies ranging from 1 to 20 MHz show a maximum LO feedthrough and image of -55 dBc and -44 dBc, respectively. The charge-based architecture spectrum is clean (see Figure 6), especially the alias. At 7 dB backoff, C-IM3 at any baseband frequency is always below -50 dBc at both 900 MHz and 2.4 GHz. As with the previous implementation, the sampling aliases are shaped by a sinc2 transfer function, which corresponds to at least 20 dB of additional attenuation compared to a conventional architecture (see Figure 7). ACLR 1 and 2 for a 20 MHz signal are -47 dB and -59 dB, respectively, and the measured EVM is 1.6 percent. At 45 MHz offset, a modulated noise power density of -159 dBc/Hz was measured at both LO frequencies (see Figure 8). What is unique is that even in backoff conditions, the noise performance is not degraded significantly, thanks to the intrinsic noise filtering capabilities of the charge-based architecture.

With the achieved out-of-band noise performance and a core area of only 0.22 mm2, the charge-based architecture achieves — to the author’s knowledge — the best out-of-band noise performance vs. area compared to other designs. ACLR and EVM performance are also among the best

Figure 8 Noise spectral density of a 2.4 GHz modulated carrier (10 MHz single tone sampled at 500 MSPS, with the baseband harmonics removed for clarity).

References

- X. He, J. van Sinderen and R. Rutten, “A 45 nm WCDMA Transmitter Using Direct Quadrature Voltage Modulator with High Oversampling Digital Front-End,” ISSCC Digest of Technical Papers, pp. 62–63, February 2010.

- V. Giannini, M. Ingels, T. Sano, B. Debaillie, J. Borremans and J. Craninckx, “A Multiband LTE SAW-less Modulator with -160 dBc/Hz RX-band Noise in 40 nm LP CMOS,” ISSCC Digest of Technical Papers, pp. 374–376, February 2011.

- O. Oliaei, M. Kirschenmann, D. Newman, K. Hausmann, H. Xie, P. Rakers, M. Rahman, M. Gomez, C. Yu, B. Gilsdorf and K. Sakamoto, “A Multiband Multimode Transmitter Without Driver Amplifier,” ISSCC Digest of Technical Papers, pp. 164–166, February 2012.

- P. Rossi, N. Codega, D. Gerna, A. Liscidini, D. Ottini, Y. He, A. Pirola, E. Sacchi, G. Uehara, C. Yang and R. Castello, “An LTE Transmitter Using a Class-A/B Power Mixer,” ISSCC Digest of Technical Papers, pp. 340–341, February 2013.

- M. Ingels, Y. Furuta, X. Zhang, S. Cha and J. Craninckx, “A Multiband 40 nm CMOS LTE SAW-less Modulator with −60 dBc C-IM3,” ISSCC Digest of Technical Papers, pp. 338–339, February 2013.

- P. Eloranta, P. Seppinen, S. Kallioinen, T. Saarela and A. Parssinen, “A Multimode Transmitter in 0.13 um CMOS Using Direct-Digital RF Modulator,” IEEE Journal of Solid-State Circuits, Vol. 42, No. 12, pp. 2774–2784, December 2007.

- M. Ingels, X. Zhang, K. Raczkowski, S. Cha, P. Palmers and J. Craninckx, “A Linear 28 nm CMOS Digital Transmitter With 2×12 Bit up to LO Baseband Sampling and −58 dBc C-IM3,” European Solid State Circuits Conference (ESSCIRC), pp. 379–382, September 2014.

- Z. Boos, A. Menkhoff, F. Kuttner, M. Schimper, J. Moreira, H. Geltinger, T. Gossmann, P. Pfann, A. Belitzer and T. Bauernfeind, “A Fully Digital Multimode Polar Transmitter Employing 17b RF DAC in 3G Mode,” ISSCC Digest of Technical Papers, pp. 376–378, February 2011.

- S.M. Yoo, J. S. Walling, O. Degani, B. Jann, R. Sadhwani, J. C. Rudell and D. J. Allstot, “A Class-G Switched-Capacitor RF Power Amplifier,” IEEE Journal of Solid-State Circuits, Vol. 48, No. 5, pp. 1212–1224, May 2013.

- P.E. Paro Filho, M. Ingels, P. Wambacq and J. Craninckx, “A Transmitter with 10b 128 MS/s Incremental-Charge-Based DAC Achieving −155 dBc/Hz Out-of-Band Noise,” ISSCC Digest of Technical Papers, pp. 164–165, February 2015.

- P.E. Paro Filho, M. Ingels, P. Wambacq and J. Craninckx, “A 0.22 mm2 CMOS Resistive Charge-Based Direct-Launch Digital Transmitter With -159 dBc/Hz Out-of-Band Noise,” ISSCC Digest of Technical Papers, pp. 250–252, February 2016.

- P.E. Paro Filho, M. Ingels, P. Wambacq and J. Craninckx, “An Incremental-Charge-Based Digital Transmitter With Built-In Filtering,” IEEE Journal of Solid-State Circuits, Vol. 50, No. 12, pp. 3065−3076, December 2015.