AMD’s latest generation Xilinx® Zynq® UltraScale+™ RFSoC has been added to the reference designs for the Evenstar open RAN (O-RAN) radio unit (RU), according to AMD and Meta Connectivity.

The Evenstar program, led by Meta Connectivity, was launched in February 2020 to develop O-RAN reference designs for 4G and 5G networks, with the goals of lower cost and more innovative cellular infrastructure. By defining standards for the network interfaces, operators are freed from being locked to end-to-end solutions offered by the three large network equipment manufacturers (NEM). According to the growing number of advocates, O-RAN will open the supply chain to companies that specialize in optimizing the individual elements of the network, from RF to software, which will encourage competition and innovation, leading to better and lower cost networks and mobile services.

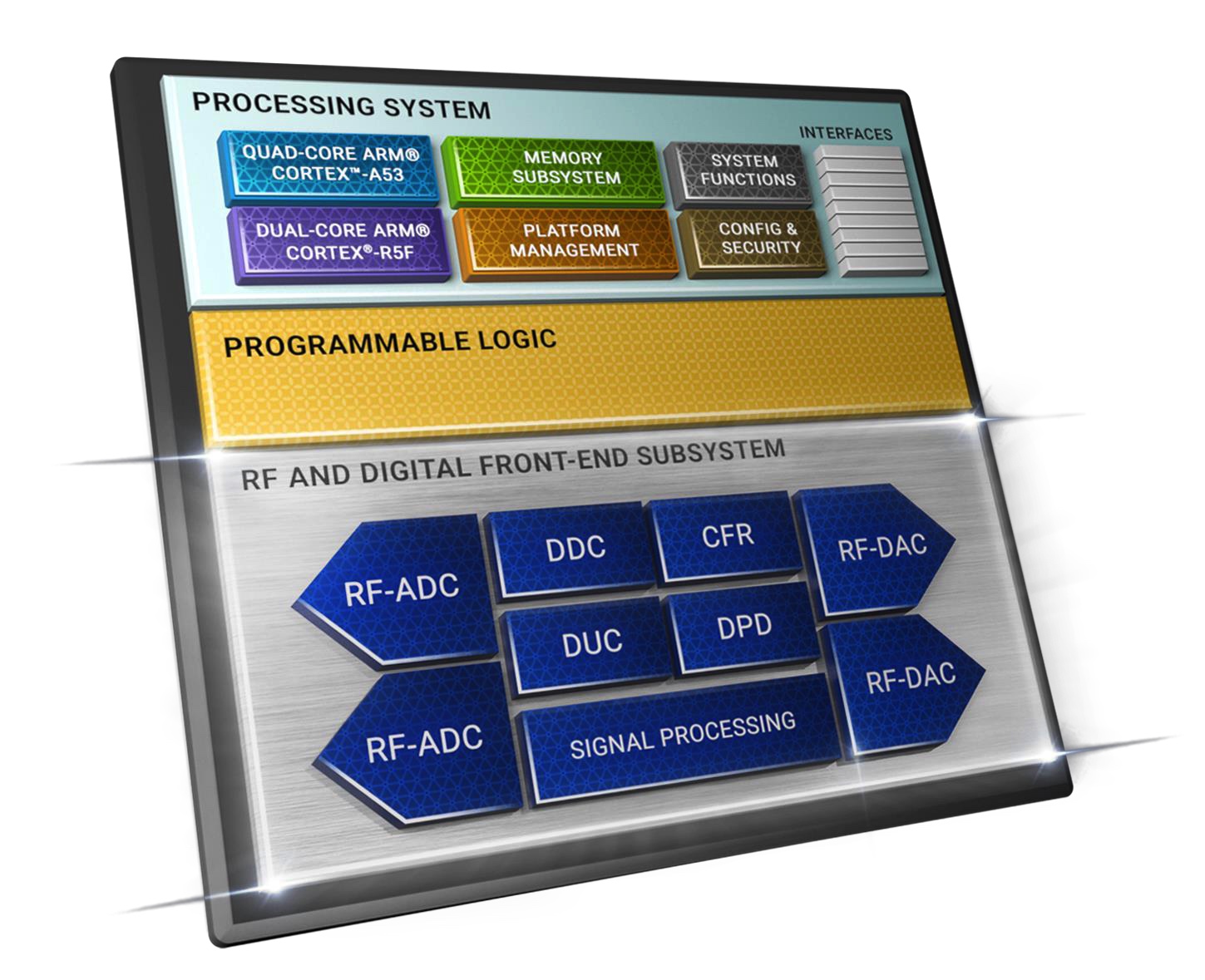

The RFSoC added to the Evenstar program — AMD’s fourth generation, which was renamed the Zynq RFSoC DFE — provides the radio subsystem for an eight transmit, eight receive (8T/8R) base station, either frequency-division or time-division duplex (FDD/TDD). Multiple DFEs can be combined to scale the base station to mMIMO, e.g., eight DFEs for a 64T/64R array and a single Versal processor for beamforming.

Simplified functional diagram of the AMD Zynq RFSoC DFE.

Simplified functional diagram of the AMD Zynq RFSoC DFE.

The DFE’s onboard analog-to-digital and digital-to-analog converters support direct sampling to 7.125 GHz with up to 400 MHz instantaneous bandwidth, enabling the IC to support all current sub-6 GHz 5G bands. The wide instantaneous bandwidth can handle multiple bands with carrier aggregation, enabling RAN sharing by several operators, even 4G and 5G simultaneously. On-chip processing includes crest factor reduction (CFR) and digital predistortion (DPD) with the capability to support 400 MHz DPD for GaN PAs.

Even with this processing power, the DFE consumes under 25 W of DC power. Gilles Garcia, the business lead for AMD’s data center and communications group says this is because 80 percent of the IC was designed as an ASIC, the remainder in programmable logic to provide flexibility.

The fourth generation version of the RFSoC was released for production in December 2021 and is being evaluated by both O-RAN and traditional NEMs.