As society connects and shares more devices and data across networks, there is unprecedented demand for technology that will help today’s system designers. While signal processing and communications designers work to define algorithms that overcome pressing challenges regarding bandwidth, security, power efficiency and coexistence, there is a void in prototyping solutions with real-world signals.

While those in industry, academia and government laboratories have turned to software defined radio (SDR) to evaluate new designs with real-world signals and conditions, the prototyping process is far from efficient. Unfortunately, existing software tools are often a bottleneck to innovation; they typically offer a disjointed, indirect design flow. In large part, the challenge emerges from the discontinuity between tools well suited for algorithm design and those required to program the hardware components of an SDR. It is precisely this discontinuity that the LabVIEW Communications System Design Suite bridges, providing a unified design flow from algorithm to hardware.

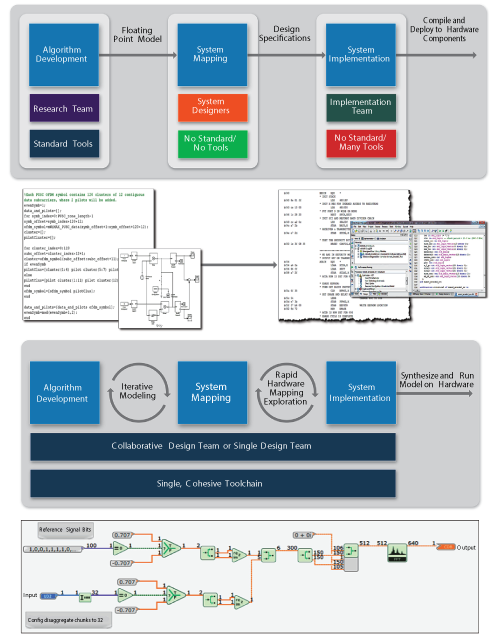

Figure 1 The traditional design process necessitates numerous tools and re-writes of an algorithm to realize a hardware prototype. This inefficient flow hinders innovation.

Designers today choose SDRs because their flexibility promises rapid prototyping. This flexibility stems primarily from computing elements that dictate the behavior of the generic, wide bandwidth RF front end multicore processors and large, user-programmable FPGAs. Unfortunately, today’s tools for programming the processors and FPGAs found on SDRs typically eradicate any hope for truly rapid prototyping. Transitioning from algorithm to implementation on a processor and an FPGA demands different specializations and tools. Design teams on the bleeding edge of various technology vectors are forcibly larger than ideal and engage in design cycles that are long and costly. The result is not a smooth, iterative prototyping process that contributes to innovation; rather, the process hinders efficiency and thwarts innovation (see Figure 1).

Figure 2 LabVIEW Communications offers a hardware-aware design environment complete with tools that validate system setup and deploy algorithms to hardware.

LabVIEW Communications offers a unified design flow for communications system prototyping. It is a single, cohesive design environment that can target both the processor and FPGA. This hardware-aware design environment includes SystemDesigner, which allows designers to validate system setup, access system documentation, describe the system architecture, configure system components, and partition and deploy algorithms to hardware. This hardware-software integration also provides access to I/O and resources, eliminating the need for middleware and driver development (see Figure 2).

The advanced compiler technology found in LabVIEW Communications enables considerable flexibility and eases algorithm descriptions dictating how they will map and perform on SDR hardware. As an example for developing signal processing algorithms, the new multirate diagram (MRD) included in LabVIEW Communications makes it possible for designers to connect processes that run at different rates without the encumbrance of handshaking, buffering and queuing data between processes. Once researchers design a signal chain in a multirate diagram, they can rely on a built-in, interactive, data-driven tool for converting the design to a fixed point and can then explore how the design performs given different requirements. Simply defining a clock rate and a throughput for the algorithm allows the underlying compiler to analyze the implementation and provide designers with timing and resource estimates specific to the SDR hardware they wish to use.

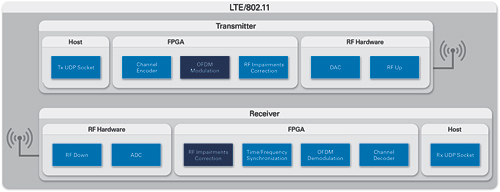

Figure 3 Application Frameworks included with LabVIEW Communications provide standards-based source code implementations for LTE and 802.11 to further accelerate designs.

Designers are liberated from having to contend with the underlying hardware architecture they deploy to. They no longer need to manually dissect a design to understand the tradeoffs between different implementations. The compiler in LabVIEW Communications does the often complex job of exploring the impact of unrolling loops, partitioning memory, modifying memory access schemes and selecting different FPGA resources/components. The designer can move forward with an implementation that best suits the design requirements based on the feedback from the compiler. As an added benefit, researchers can achieve considerable reuse as the core algorithms are defined in higher level languages, and the implementation is derived from the design requirements that are imposed upon the algorithm.

Users can rely on new Application Frameworks available with LabVIEW Communications to further expedite their design cycle. Application Frameworks provide documented, modifiable, standards-based source code for LTE and 802.11 PHYs. Designers can focus their efforts on the specific components to improve over existing LTE and 802.11 designs, instead of spending time building the requisite infrastructure needed to properly test the novel algorithms (see Figure 3).

Today’s system designers require a design flow that realizes the true potential of SDRs for rapid prototyping. LabVIEW Communications provides a seamless path from algorithm to prototype, helping designers innovate faster. Researchers have access to intuitive, high-level languages that enable efficient algorithm design and system abstraction. The hardware-aware nature of the software with SDR hardware allows for accurate, real-world I/O integration. LabVIEW Communications will help designers outpace competitors in the race to define standards for 5G and other future communications systems.

National Instruments

Austin, Texas

www.ni.com/labview