In this article, the evolution of the Doherty Power Amplifier (DPA) through its first seventy-five years is presented. The aim is to explain why this architecture is still used to realize very advanced power amplifier stages for wireless systems. To this purpose, a review of the DPA principle of operation, together with a benchmark of the state of the art results, realization methods and fields of application, is reported.

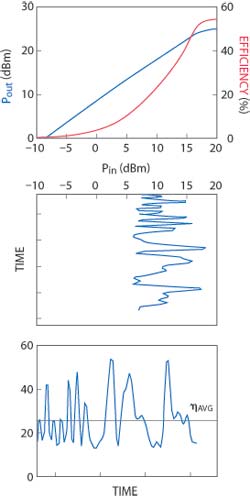

Fig. 1 Average efficiency using traditional PA.

The idea behind the power amplifier architecture, which nowadays is identified as the Doherty Power Amplifier (DPA), was proposed to the world by W.H. Doherty many decades ago. The original paper, entitled “A New High Efficiency Power Amplifier for Modulated Waves” was published in September 1936.1 Thus, the DPA has just celebrated its first seventy-five years of age.

The last sentence of that old paper was: “The new amplifier is believed to offer a most logical and practical solution to the problem of efficient operation of high power transmitters.” The prediction expressed by W.H. Doherty with these few words came true. In fact, even though actual systems are extremely different with respect to the first broadcasting transmitters, in terms of active device technologies, required power levels and adopted modulation schemes, the DPA seems to remain the best candidate to realize power amplifiers (PA) for modern and future generations of wireless systems.

In fact, the increasing complexity of modulation schemes, used to achieve higher and higher data rates, creates the need for PAs able to manage signals with a large time-varying envelope. The resulting peak-to-average power ratio (PAPR) of the involved signals critically affects the average efficiency achievable with traditional PAs. As schematically reported in Figure 1, such high values of PAPR imply a large back-off operating condition, dramatically reducing the average efficiency levels attained by using traditional PA solutions. In order to stress this effect, it is useful to refer to an ideal Class B PA, delivering an efficiency of 78.6 percent at its maximum output power, while only 25 percent at 10 dB of back-off. Therefore, when dealing with an amplitude modulated signal, it is more practical to refer to the average efficiency, which is defined as the ratio of the average output power to the average supply DC power. Clearly the average efficiency depends on both the PA instantaneous efficiency and the probability density function (PDF) of the signal. Therefore, to obtain high average efficiency when time-varying envelope signals are used, the PA should work at the highest efficiency level in a wide range of its output power.

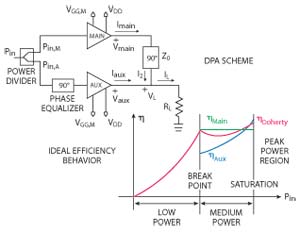

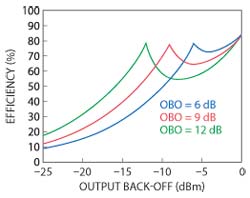

This kind of requirement represents the main feature of the DPA architecture, whose theoretical efficiency behavior is shown in Figure 2. The region with almost constant efficiency identifies the DPA output back-off (OBO) range, and it is usually fixed according to the PAPR of the signal to be amplified.

DPA Approaches

A typical DPA is composed of two active devices, namely main and auxiliary, an impedance inverter network (IIN), a phase compensation network (PCN) and an uneven input power splitter (IPS). The DPA is based on the idea to modulate the load of the main device, in order to force it to operate at its maximum efficiency condition for a pre-determined range of input power levels. Such an action is performed by exploiting the active load concept, by using the auxiliary device and exploiting the IIN properties. According to this solution, a suitable current supplied by the auxiliary amplifier in the output load dynamically modulates the load seen by the main device coherently with the input power levels.

In the first DPA implementation,1 both devices were biased in Class B condition (hereafter referred to as B-B DPA). However, the B-B configuration implies the critical issue to maintain the auxiliary off along the entire low-power region, which solution was left to “one of the many practical solutions,” as indicated in the original Doherty paper. Consequently, it becomes mandatory to complicate the hardware implementation using a switching circuitry to control the on-off auxiliary condition. In order to avoid such criticisms, a proper Class C bias condition for the auxiliary device has been adopted. However, in this case, the input power splitter dimensioning becomes a further critical design key aspect.21

Fig. 2 Typical DPA efficiency behavior vs. output power.

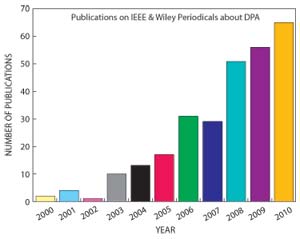

Fig. 3 DPA publications vs. years.

Finally, a pure Class B bias condition for the main device does not seem to be advisable, due to the large cross-over distortion. To avoid this further drawback, a Class AB bias condition for the main device is preferred, resulting in a small reduction of the efficiency as compared to a pure Class B, but with a significant improvement in the overall linearity.

Nowadays, the actual DPAs employ Class AB (Main) and Class C (auxiliary) bias conditions (hereafter referred to as AB-C DPA). Consequently, the characteristics and values of each DPA elements have to be carefully dimensioned and designed since they are strictly related to each other.

Thanks to the huge work done by the scientific community, several innovations regarding the DPA have been introduced and validated, mostly devoted to finding advanced design methodologies to increase the achievable DPA performances. As an example, the existing theoretical gap between the B-B DPA and the AB-C DPA has been filled.16 In this article, the role of each elements used in a typical DPA architecture and how they have to be dimensioned, considering their mutual dependence, has been highlighted and clarified.

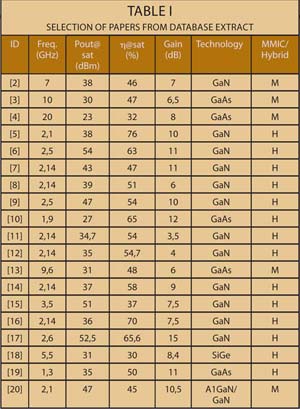

Benchmark of the State of the Art

Figure 3 shows the number of scientific papers focused on the DPA architecture over the years, from 2000 to 2010. From it, it is possible to have an idea on the increasing attention to the DPA architecture in the last few years. In fact, in 2000, only a few papers have been published on DPA, while in 2010, 65 scientific papers have been published by journals edited by IEEE and Wiley.

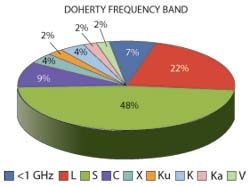

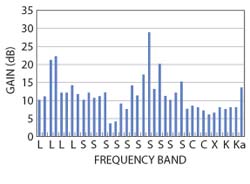

In order to benchmark the DPA architecture, an extensive database with more than 50 scientific papers has been created. However, to avoid exceeding the article maximum length, it was possible to report only a selection2-20 (see Table 1). From the collected data, it is evident that the DPA architecture is usually adopted in telecommunication systems for both handsets and base station terminals. In particular, it is frequently employed in UMTS and WiMAX systems and, with minor rate, in WiFi, WLAN, WiBro and LTE applications. This observation is also confirmed by Figure 4, where the numbers of realizations found in literature are classified as a function of their frequency band. As can be noted, almost 50 percent of DPA realizations are in S-Band (2 to 4 GHz), where the most important wireless systems are located.

Fig. 4 Frequency applications for DPAs.

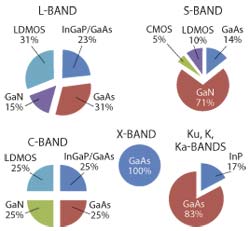

Fig. 5 Active device technologies for DPAs.

Figure 5 shows the active device technologies used to design DPAs for each frequency band. As can be observed, in S-Band, almost the totality of DPAs is realized using GaN technology and, as will be highlighted later, in hybrid form. In fact, thanks to the high power capability of GaN devices and the fast prototyping offered by the hybrid structure, it is much easier to reach high power level together with a simpler circuit layout.

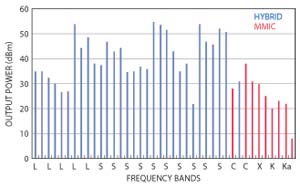

Fig. 6 Hybrid vs. MMIC DPA realizations.

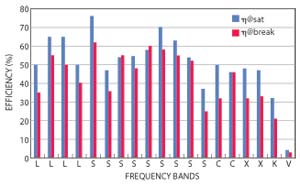

Fig. 7 Efficiency levels of DPA realizations.

Figure 6 shows the output power levels achieved by DPAs realizations as a function of frequency bands, while distinguishing between MMIC and hybrid forms. As stated before, the hybrid form is almost always used up to S-Band while, for upper frequencies, MMIC technology is preferred. Moreover, a considerable number of realizations achieved output power levels higher than 50 dBm.

Considering the key feature of a DPA, Figure 7 shows the achieved efficiency levels corresponding to both saturation and break point conditions, as a function of frequency bands. It is important to emphasize that the break point represents the power level at which the auxiliary amplifier is turned on.

Typically, and for all the realizations reported, the break point is located at 6 dB of OBO. As can be noted, with respect to a traditional single ended PA, the DPA architecture assures high efficiency also in back-off, that is a fundamental characteristic for systems that deal with time varying envelope signals.

Fig. 8 MMIC DPA for X-Band application.

Fig. 9 S-Band hybrid DPAs using GaN technology.

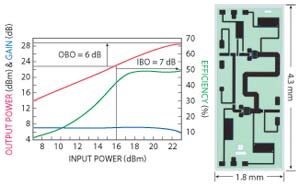

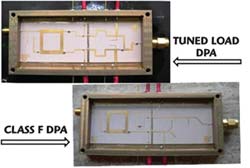

As an example of MMIC DPA, Figure 8 shows a photo and the corresponding experimental results of a GaAs MMIC DPA realized for X-Band application. Analogously, Figure 9 shows the photos of two DPAs for S-Band applications, using GaN technology realized in hybrid form. The first DPA has been designed assuring a tuned load harmonic configuration for both main and auxiliary devices.16 For the other one, with the aim to further increase the efficiency level achieved by the DPA at the break point, a Class F harmonic configuration has been adopted for the main device.12 Regarding the design of the auxiliary amplifier, also in this case, a TL configuration has still been considered to optimize its performance. In fact, due to the Class C biasing condition, the adoption of other different HT strategies (including the Class F one) would result in a detrimental effect for the auxiliary device performance.12 Both are designed using a GaN HEMT (1 mm of gate periphery) as the active device to operate at 2.14 GHz, assuring an almost constant efficiency over the usual OBO range of 6 dB.

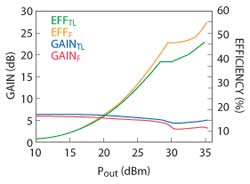

A comparison of the obtained experimental results from the two DPAs is shown in Figure 10. As can be noted, the expected (roughly) 15 percent improvement in output power and drain efficiency, when using a Class F configuration with respect to its TL counterpart, has been experimentally demonstrated.12 On the other hand, one of the main drawbacks of the DPA architecture is related to its intrinsic lower power gain, with respect to the nominal value assured by the main amplifier alone. Figure 11 shows the gain level achieved by the realizations included in our database as a function of frequency bands.

Fig. 10 F-DPA and TL-DPA performance.

Fig. 11 Gain levels of DPA realizations.

As can be noted, few realizations have a gain higher than 15 dB, despite the low frequency band and the use of active devices with high available gain levels. Typically, the realizations with higher gain include a driver to increase this feature, with a consequent reduction of the overall efficiency level. Generally speaking, while comparing the DPA gain with the one achievable through a standard PA, designed by using the same active devices, a drop of about 4 to 6 dB is observed. This decrease can be ascribed to both the Class C bias condition of the auxiliary amplifier and the uneven input power splitter. The former is needed to assure the automatic turning on condition at the break point, while the latter is necessary to guarantee the correct dynamic evolution, from the break point to saturation.21

Fig. 12 F-DPA and TL-DPA performance.

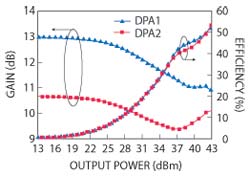

In terms of efficiency, this effect could be a problem when, for instance, the DPA has to be integrated in a transmitter chain. In fact, in those cases, a driver stage could be necessary to assure the requested gain level. These driver stages are usually designed to operate as linear systems, so their efficiency is typically very low. Therefore, the efficiency of the overall chain is similar to the one of the DPA if, and only if, its gain is very high. For this reason, in high frequency applications, where the active devices for power applications usually have an available gain lower than 15 dB, a gain drop of about 4 to 6 dB for the power stage becomes unacceptable. For practical uses, new ideas to overcome the gain problem are under investigation. For instance, it has been demonstrated that the adoption of different drain bias voltages for the main and auxiliary device could be useful to increase the gain of the overall DPA.7 In this case, to demonstrate the reliability of the proposed design methodology, two different DPAs have been designed: one with the same bias voltages for main and auxiliary devices (DPA1), and a second one (DPA2) that uses different drain bias voltages according to the guidelines derived previously.7

For the design, an LDMOS device, provided by Freescale Semiconductor, has been used and the operating frequency of 2.14 GHz has been assumed. Figure 12 shows the comparison between the performance obtained from both prototypes. As can be noted, both DPAs reach the same saturated output power level (43 dBm), with a quite similar efficiency behavior. However, it can be noted that an increase of roughly 2 dB in power gain has been obtained with DPA2. For both DPAs, the efficiency is higher than 40 percent with an OBO of 6 dB.

Fig. 13 Efficiency behavior of DPAs with different OBO.

Another drawback of the standard DPA architecture becomes evident when the PAPR of the signal to be amplified is larger than 8 to 9 dB. In fact, referring to Figure 13 where the efficiency behaviors of DPAs with different OBOs are plotted; in the case of OBO =12 dB, the achievable average efficiency is dramatically reduced. Therefore, new solutions to overcome this further drawback are also under study, as the multi-stage or n-stage, sometimes also named multi-way DPA.22

Finally, looking at the DPA topology, it is possible to note that it is intrinsically based on many narrow band components, like the IIN, the IPS and the PCN. This aspect restricts the DPA potentialities as the best solution for power stage in modern communication systems. In fact, one of the goals of the new systems is to simultaneously operate with more communication standards (such as UMTS, WiMAX, WiFi, etc.). Since each standard has its frequency band, transmitters with multi-band frequency capability become mandatory. Thus, ideas to alleviate such weakness are needed. A possible solution has been reported8 where the design of a dual-band DPA is demonstrated.

Conclusion

In this article, the evolution of the DPA through its first seventy-five years has been presented. The reasons why this architecture is still popular to realize power amplifier stages for wireless systems have been highlighted. A review of the DPA principle of operation, together with a benchmark of state of the art realization methods and fields of application has been reported.

References

- W.H. Doherty, “A New High Efficiency Power Amplifier for Modulated Waves,” Proceedings of the Institute of Radio Engineers, Vol. 24, No. 9, September 1936, pp. 1163-1182.

- R. Quaglia, V. Camarchia, M. Pirola, S. Donati Guerrieri, R. Tinivella, G. Ghione and M. Pagani, “7 GHz GaN MMIC Power Amplifier for Microwave Radio Links with 45 Percent Drain Efficiency in a Wide Power Range,” Proceedings of the 2010 Workshop on Integrated Nonlinear Microwave and Millimeter Wave Circuits (INMMiC), pp. 160-163.

- P. Colantonio, F. Giannini, R. Giofrè and L. Piazzon, “An X-Band GaAs MMIC Doherty Power Amplifier,” Proceedings of the 2010 Workshop on Integrated Nonlinear Microwave and Millimeter Wave Circuits (INMMiC), pp. 41-44.

- C.P. McCarroll, G.D. Alley, S. Yates and R. Matreci, “A 20 GHz Doherty Power Amplifier MMIC with High Efficiency and Low Distortion Designed for Broad Band Digital Communication Systems,” 2000 IEEE MTT-S International Microwave Symposium Digest, Vol. 1, pp. 537-540.

- A.Z. Markos, P. Colantonio, F. Giannini, R. Giofre, M. Imbimbo and G. Kompa, “A 6 W Uneven Doherty Power Amplifier in GaN Technology,” 2007 European Conference on Wireless Technology Proceedings, pp. 379-382.

- H. Sano, N. Ui and S. Sano, “A 40 W GaN HEMT Doherty Power Amplifier with 48 Percent Efficiency for WiMAX Applications” 2007 IEEE Compound Semiconductor Integrated Circuit Symposium Proceedings, pp. 1-4.

- P. Colantonio, F. Giannini, R. Giofrè, L. Piazzon and M. Piacentini, “A Design Approach to Increase Gain Feature of a Doherty Power Amplifier” 2009 Proceedings of the European Microwave Integrated Circuit Conference, pp. 25-28.

- P. Colantonio, F. Feudo, F. Giannini, R. Giofrè and L. Piazzon, “Design of a Dual-Band GaN Doherty Amplifier” 2010 Proceedings of the 18th International Conference on Microwave Radar and Wireless Communications, Vol. 2, pp. 483-486.

- A.Z. Markos, K. Bathich and G. Boeck, “Design of GaN HEMT Based Doherty Amplifiers” Proceedings of the 11th Annual Wireless and Microwave Technology Conference, 2010, pp. 1-5.

- S. Bousnina, “Maximizing Efficiency and Linearity” IEEE Microwave Magazine, Vol. 10, No. 5, 2009, pp. 93-98.

- P. Colantonio, F. Giannini, R. Giofrè and L. Piazzon, “Doherty Power Amplifier and GaN Technology” 2010 Proceedings of the 18th International Conference on Microwave Radar and Wireless Communications, Vol. 2, pp. 487-490.

- P. Colantonio, F. Giannini, R. Giofrè and L. Piazzon, “Theory and Experimental Results of a Class F AB-C Doherty Power Amplifier,” IEEE Transactions on Microwave Theory and Techniques, Vol. 57, No. 8, August 2009, pp. 1936-1947.

- P. Colantonio, F. Giannini, R. Giofrè, M. Piacentini and L. Piazzon, “GaAs MMIC Doherty Power Amplifier with Asymmetrical Drain Bias Voltage,” 2010 Proceedings of the 18th International Conference on Microwave Radar and Wireless Communications, Vol. 2, pp. 479-482.

- P. Colantonio, F. Giannini, R. Giofrè and L. Piazzon, “GaN Doherty Amplifier With Compact Harmonic Traps,” Proceedings of the 2008 European Microwave Conference, pp. 1553-1556.

- J.H. Moon, J.H. Kim, I. Kim, Y.Y. Woo, S.H. Hong, H.S. Kim, J.S. Lee and B. Kim, “GaN HEMT Based Doherty Amplifier for 3.5 GHz WiMAX Applications,” Proceedings of the 2007 European Conference on Wireless Technologies, pp. 395-398.

- P. Colantonio, F. Giannini, R. Giofrè and L. Piazzon, “The AB-C Doherty Amplifier: Part II Validation,” International Journal on RF and Microwave Computer-Aided Engineering, Vol. 19, No. 3, May 2009, pp. 307-316.

- H. Deguchi, N. Ui, K. Ebihara, K. Inoue, N. Yoshimura and H. Takahashi, “A 33 W GaN HEMT Doherty Amplifier with 55 Percent Drain Efficiency for 2.6 GHz Base Stations,” 2009 IEEE MTT-S International Microwave Symposium Digest, pp. 1273-1276.

- H. Liu and T. Yoshimasu, “A 5.5 GHz SiGe HBT Doherty Amplifier Using Diode Linearizer and Lumped-element Hybrid Coupler,” Digest of Silicon Monolithic Integrated Circuits in RF Systems, 2006.

- D.M. Upton and P.R. Maloney, “A New Circuit Topology to Realize High Efficiency, High Linearity and High Power Microwave Amplifiers,” 1998 Radio and Wireless Conference Digest, pp. 317-320.

- M.J. Poulton, W.K. Leverich, P. Garber, J.B. Shealy, R. Vetury, J.D. Brown, D.S. Green, S.R. Gibb and D.K. Choi, “AlGaN/GaN 120W WCDMA Doherty Amplifier with Digital Pre-Distortion Correction,” 2006 Annual Wireless and Microwave Technology Conference Digest, pp. 1-3.

- P. Colantonio, F. Giannini, R. Giofrè and L. Piazzon, “The AB-C Doherty Amplifier: Part I Theory,” International Journal on RF and Microwave Computer-Aided Engineering, Vol. 19, No. 3, May 2009, pp. 293-306.

- R. Gajadharsing, “3-Way Doherty Amplifier with Minimum Output Network,” International Patent No. WO 2009/081341 A1, June 2, 2009.