Figure 1 Data processing requirements reach new domains.

Developing the next generation of mission-critical defense systems, including beamforming, radar and electronic warfare (EW), requires processing higher volumes of sensor data in harsh and size, weight and power (SWaP)-constrained environments. Defining the incoming signal and transforming the accompanying data into actionable intelligence requires more from the sensor and the system. Traditionally, these operations are complex and add significant latency to effectively respond to emerging threats.

As sensors collect ever-increasing volumes of data, the expectations on edge processing technology also increase. This next-generation of processing components must not only be small and rugged, able to function in a fighter jet or on a joint light tactical vehicle, but they must also deliver enough processing power to enable sophisticated artificial intelligence (AI)-based applications like image recognition and cognitive EW. The result is that edge computing has moved data processing far beyond a ground-based command and control center as shown conceptually in Figure 1.

Compute-Intensive Solutions At The Tactical Edge

There is no doubt that processing technology needs to adapt to handle the massive influx of data to create faster, stronger and more capable systems at the edge. Driven by the enormous market forces of worldwide electronics demand, AMD offers the Adaptive Compute Acceleration Platform (ACAP). This platform provides a different type of semiconductor architecture that is fueling a generational leap in edge computing capabilities for defense applications.

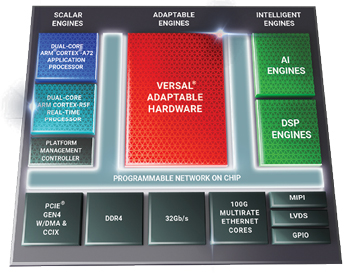

Figure 2 The AMD Versal AI Core ACAP.

Part of the AMD Xilinx Versal portfolio, the Versal AI Core ACAP is more than just another field programmable gate array (FPGA) or system on chip (SoC). It combines multiple styles of computing in a single silicon chip, making it a true heterogeneous processor. It is fabricated with state-of-the-art 7 nm technology, incorporating three different types of compute engines. As an adaptive SoC, an ACAP can be given a new hardware configuration to adapt to application requirements, providing a unique differentiator from CPUs, GPUs and application specific standard products, which all have fixed hardware architectures.

For defense systems, perhaps the most exciting feature of ACAP is that it can support adding AI capability to a host of edge applications. And this new processing technology also helps military systems in several other ways. The AMD Versal AI Core ACAP is shown in Figure 2. It combines multiple styles of computing in a single silicon chip, making it a true heterogeneous processor and it sets the stage for a new wave of compute-intensive defense applications.

Making ACAPs Accessible For Aerospace And Defense Systems

The Versal platform includes software development tools and offers flexibility that matches the device’s multiple engine types. There are a range of options, so developers can use familiar tools and languages. Embedded software developers can program in C using the AMD Vitis software platform and hardware engineers can continue to use AMD’s Vivado tools to program in VHDL or Verilog.

Additionally, AI developers can use machine learning (ML) frameworks such as TensorFlow or PyTorch and target their C++ algorithms and Python data flows to the Versal ACAP. This can be done without using the traditional tools needed to write Register Transfer Level (RTL), a design abstraction used to model a digital circuit. In the case of an ASIC or an FPGA, an RTL description can usually be directly translated to an equivalent hardware implementation file.

Figure 3 The Mercury SCFE6931 ACAP processing module.

The industry’s first deployable heterogeneous processing module using the Versal AI Core ACAP is the rugged SCFE6931. This is a single-slot, 6U OpenVPX form factor product designed to support multiple high-reliability cooling options. With two Versal AI Core devices, it delivers a tremendous level of flexible processing power to edge applications. To jump-start development, the low-cost 6U VPX Model 8258 enables developers to build, run and debug applications on the SCFE6931 Dual Versal ACAP processing module shown in Figure 3. SWaP-optimized and ruggedized deployable ACAP-based solutions, like Mercury’s SCFE6931, deliver a tremendous level of flexible processing power to edge applications.

Defining Industry Challenges

Mission-critical defense systems now employ countless sensors. Many collect imaging data, centered on the visual spectrum, but extend into the infrared and ultraviolet ranges. Others track electromagnetic communications or radar input ranging from traditional frequencies through mmWave (100 MHz through 50 GHz) ranges. Still others monitor physical vibrations for sonar or voice recognition. In every one of these areas, applications are requiring expanded capabilities, like more detailed images, the ability to track more targets and a comprehensive view of the radio spectrum.

This data is complex. Both radar and EW sensors are reaching new levels of sophistication and returning large amounts of streaming data. Efficiently exploiting this data requires powerful processing technology to translate incoming signals and extract what is needed most.

The environments are harsh. The demand for processing at the edge, where systems must withstand environmental elements such as extreme temperature, moisture and vibration, is constantly being pushed further. Additionally, this capability must be achieved without sacrificing a SWaP focus.

Processing speed is increasing. GPUs, CPUs and traditional memory schemes are no longer sufficient to handle the increasing high speed data streaming needs and the low latency demands critical for real-time sensor processing. New sensors must operate with greater precision (bit-depth) and speed (data rate) to generate an expanded data stream from each node. When that effect is combined with a continual increase in the number of deployed sensors, the result is a geometric increase in sensor data volumes, to the point where some individual systems must deal with Tb/s of input.

Figure 4 Complex waveforms require edge data processing.

Victory on the twenty-first century battlefield now requires processing vast quantities of information in real-time. More detailed imagery is needed to enable better decision-making in tactical command centers. Radar tracking must be able to monitor more targets across expanded distances and EW systems will need to deal with an increasingly complex range of waveforms, like the one shown conceptually in Figure 4, that will be generated by clever adversaries. Applying edge data in real-time means enhanced decision-making and more successful missions.

True Heterogenous Processing

Incorporating three different types of compute engines, each ACAP device includes scalar engines, programmable logic and intelligent engines, all connected by an extremely high bandwidth network-on-chip (NoC). Multiple compute engine types are designed into the ACAP, because no single style of processing is capable of optimally performing all the tasks involved in a sophisticated edge application.

Scalar engines function like traditional CPUs and they are ideal for complex decision-making and control. The Versal AI Core ACAP includes four of these as well as two low-power Arm CortexR5F real-time processors and two full-power domain Cortex-A72 cores, supported by a system memory management unit. These processing engines are vital for managing and responding to human interfaces, controlling multi-mission system behavior and countless other operations that involve choosing between multiple options.

Programmable logic, also referred to as adaptable engines, adds the flexibility to handle a diverse set of computationally demanding algorithms. Included are FPGA structures, with 1.5x the lookup tables of AMD’s high-end Virtex UltraScale+ FPGA, as well as programmable I/O and a customizable memory hierarchy of block RAM and UltraRAM. Just like FPGAs, adaptable engines provide highly efficient signal processing for radar and EW applications.

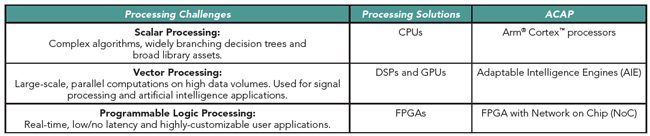

Intelligent engines are optimized for advanced signal processing, like linear algebra and matrix math, which are well suited for 5G wireless systems and AI inference. The ACAP contains DSP and AI engines. The DSP engines function like traditional digital signal processors and they are optimal for certain kinds of signal processing like routines that use context switching. The AI engines, similar to advanced GPUs, comprise vector processors for fixed and floating-point operations, a scalar processor as well as dedicated program and data memories. The vector processors in the AI engines deliver fast manipulation of image pixels as well as high performance for ML and inference algorithms in AI-based applications. The chart in Figure 5 shows some of the processing challenges and solutions that ACAP addresses. Multiple compute engines designed into the ACAP enable powerful processing in sophisticated edge applications.

Figure 5 How ACAP addresses processing challenges.

Keep The Data Moving

High performance memory access is critical to ensuring that applications can deliver a low latency, deterministic response. The ACAP addresses this with an on-chip, cacheless memory hierarchy consisting of block RAM, UltraRAM and accelerator RAM; all levels of the hierarchy are essentially shared RAM. The accelerator RAM, introduced in the Versal AI Core series, enables multiple application datasets to be stored directly on-chip, reducing both power consumption and latency by avoiding the need to access off-chip memory.

Having a variety of processing engines is only useful if they are processing data in parallel and not stalled, so managing I/O bottlenecks is critical. The ACAP’s hardened NoC can be programmed to support flexible data flows between the full range, high speed I/Os and the various types of computing engines. The NoC programmability extends to addressing different levels of throughputs, latencies and even bit widths, in the event of multiple algorithms on a single chip being optimized for different resolutions.

Functionally, the NoC is a packet switch network that performs high speed, point-to-point hops to move data around the device. Even without exploiting its inherent parallelism, the NoC is capable of data bandwidths exceeding 2 Tb/s, with much greater data transport capacity if the application design mapping exploits parallelism. This level of on-chip bandwidth is critical for low latency performance in applications like active electronically scanned array radars that must process multiple data streams concurrently. It is also important in complex AI-enhanced EW applications that first use FPGA structures to apply signal processing algorithms to a captured signal and then must move the processed data to an AI engine where other algorithms implement analysis and response.

Ensuring System Security

With edge processing comes an increased concern for data safety. Cyberattacks and threats to data integrity are constantly on the rise, so ACAPs are designed with safety features built in from the ground up. The Versal architecture is partitioned with functional hardware features in each domain as well as global resources to monitor and eliminate common cause failures. The robust set of security features within the ACAP architecture includes:

- Hardware root of trust

- Boot time firmware and image authentication

- SCA-resistant crypto engines to decrypt images

- Debug security

- Key management

- Secure and measured boot with remote attestation

- Attack protection

- Tamper detection and protection

- Run-time security

- Trust zone and trusted execution environment

- Memory and peripheral protection

Improved Intelligence in Deployed Applications

Defense applications usually involve multiple processing steps as sensor data is manipulated, analyzed and used to drive a response. For example, in EW systems, multi-step signal processing algorithms are used to extract waveforms from an antenna’s input, then those waveforms are analyzed to find signals of interest. New advanced EW systems will add another processing level by using AI to create, in real-time, countermeasures addressing those signals of interest. This type of application is often referred to as cognitive EW.

Optimized execution for each step requires a specific type of processor. In currently deployed systems, this is accomplished by using a set of specialized processor boards with data moving between the boards using system backplane interconnects. These types of systems cannot meet the SWaP constraints of small platforms on the edge, while latency limits are dictated by the system-level interconnect.

With an ACAP, this type of application processing can now be implemented within a single chip. All the processing engines can operate in parallel on a pipelined data stream that moves between engines using the NoC. On-chip data movement latency is at a level far beyond the capability of even the fastest multi-board system.

Powerful Processing at the Edge

Similar forms of advanced functionality, powered by AI, can be envisioned across a range of applications. Image recognition located next to the optical and infrared sensors in perimeter security systems is one example. Voice recognition attached to microphones would further enhance these systems.

Another image recognition example involves UAV data collection. For example, a surveillance UAV may fly an 18-hour mission, imaging disputed terrain, with only five minutes of that imaging showing anything of interest to analysts. Having an onboard AI capability that could identify, extract and transmit that small section of collected data would enable better command decisions and faster responses.

Entirely new applications will also become possible. Autonomous ground vehicles are a DOD goal. Achieving this goal will allow supply convoys in future conflicts to operate without human drivers, reducing potential casualties. An ACAP is well equipped to process the data from multiple sensors, combine that sensor data with map data and then use its intelligence engines to execute AI algorithms for navigation and vehicle control.

Meeting the Military’s Complex Data Demands

Exploding sensor data volumes, the need for ever-faster response times and sophisticated sensor-fusing applications are all driving the need for powerful processing capabilities placed on the edge, adjacent to the sensors. In addition to the processing of more data at the edge, many next-generation deployed systems will need AI capabilities to maintain dominance on the electronic battlefield. And the next generation of edge processors must also be able to support these AI applications with both low latency and response flexibility. Edge deployment also means operating in exposed and harsh environments. Sensor edge processing systems must be designed and packaged to be extremely rugged and able to withstand shock, vibration and temperature extremes.

With rugged, deployable ACAP-based solutions being brought to market, a new level of computational performance has been unleashed for the next era of specialized computing. By combining multiple types of processing elements into a single architecture, this highly dense, next-generation processing technology enables a whole new category of dramatically faster devices that step beyond the current CPU/GPU/FPGA paradigm.