Today's wireless world requires unrelenting technological innovation. From cell phones that take and send photos to homeland security, the demands on wireless designers for increasing complexity at lower prices and faster time-to-market are immense.

Advances in electronic design automation (EDA) over the last decade have made possible dramatic improvements in quality and product-to-market for designers of digital integrated circuits (IC). Integrated design solutions combining logic synthesis and advanced place-and-route capabilities have enabled the digital semiconductor industry to deliver complicated multi-million gate application-specific integrated circuits (ASIC) and systems-on-a-chip (SoC). EDA tools for RFIC design and production have not, unfortunately, yielded the same levels of improved capacity or performance. By comparison, analog and RF EDA tools have languished in a relative "stone age" in terms of engineering productivity, and the basic design methodologies have remained largely unchanged. The design of today's complex RFICs presents a unique set of design challenges that render many of the semi-automated approaches for lower frequency analog or digital design useless. Some of these challenges include electromagnetic (EM) coupling, device and process variations, and interconnect modeling. RFIC designers are also confronted with additional issues that stem from working with newly introduced, exotic semiconductor materials such as silicon germanium (SiGe) and RF complimentary metal-oxide semiconductor (CMOS).

The use of innovative materials, when combined with both high power and high frequency of operation, presents unique problems when extracting accurate models. In addition, with all of the interactions between transmission lines, engineers would never rely on an automated synthesis or placement and routing tool for their RFIC designs.

Traditional EDA frameworks have been open to integrating third-party technology. Unfortunately, the RF and microwave EDA industry has not enjoyed open integration between vendor tools, forcing users into one of two choices. Either they must buy a complete solution from a single vendor, or, alternatively, many companies have resorted to stitching tools together from various vendors to create a customized in-house solution.

A typical RFIC design flow, shown in Figure 1 , indicates where hand-offs occur and where iteration loops can cause potential delays, or, worse, introduce errors. Under this fragmented approach, designs are often entered once into a circuit simulator and then manually re-entered into the layout system's schematic editor for documentation purposes before creating the layout itself. As shown in the RFIC design process, the final verification and design-rule-checker (DRC) step may catch mask errors, but the numerous iterations between the layout tool and the circuit simulator can delay product delivery or increase fabrication costs. This fragmentation, partially the result of closed EDA systems, has hampered the growth and evolution of the microwave semiconductor industry while making the designer's job more tedious and error-prone.

The good news is this legacy methodology is beginning to change as new EDA tools and partnerships that produce foundry libraries converge to provide the long-awaited boost in high frequency IC development. The Analog Office™ 2003 design suite from Applied Wave Research Inc. (AWR™) has been developed specifically to streamline the RFIC design process (see Figure 2 ). The software addresses the three essential keys to improved productivity - accuracy, integration and openness.

EDA Integration

For most digital or low frequency analog electronic designs, the layout process is distinct and independent from the simulation process. At RF frequencies, however, layout is so critical to performance that it must be an integral part of the simulation process.

As previously outlined, legacy EDA tools fail to provide the integration necessary for accurate, reliable RFIC design. In order to provide a robust integrated environment for RFIC design, a radically different approach is required that offers a departure from the architecture of traditional EDA tools. Analog Office 2003 software uniquely addresses this requirement. It was developed from the ground up using a revolutionary object-oriented, open architecture that facilitates a "layout centric" view of the design. The architecture, depicted in Figure 3 , is a native Windows application that leverages Microsoft technology by using interoperable binary software components called component object models (COM). COMs provide a solid foundation for higher level software integration by enabling the different tools within the Analog Office design suite to work together seamlessly and reliably. Using the Analog Office unified design environment enables analog and RFIC designers to interact with a comprehensive set of time- and frequency-domain simulation and analysis capabilities. The system allows designers to capture the product idea or concept at the system-level design or circuit level, while being able to simulate and analyze the entire system at both system and circuit levels.

The Analog Office integrated EDA solution illustrated in Figure 4 combines an advanced IC layout editor with system, circuit and EM analysis tools that all leverage a single object-oriented database. The schematic and layout data are implicitly synchronized by virtue of the underlying product architecture, without the need for netlists or design synchronization routines.

This advanced computer science results in a highly functional and very fast RFIC design tool. The Analog Office product is ideal for handling both the electrical and physical layout of RFIC designs because the two representations are structured in software as "views" of the same underlying data structures. The Analog Office suite was designed around a single unified database that is always consistent between schematic, simulation and layout views. The layout editor directly drives the simulation engine without back annotation, forward annotation, or any need for design synchronization routines. The simulator uses an incremental computation algorithm that enables microwave circuits to be "tuned in real-time." Users can physically re-route transmission lines and literally stretch layout cells, and the simulation output can be updated virtually instantaneously. Schematic, simulation and layout data are always consistent because of the implicit connection through a common database.

RF Closure

Just as deep submicron interconnect and gigahertz clock frequencies have driven the need for better timing closure in digital design, high frequency impairments are forcing the need to obtain "RF closure" between the RFIC's system and circuit, electrical and physical, and design and test activities before commitment to costly IC implementation. As Figure 5 illustrates, RF closure is the completion process by which a wireless IC is designed and verified to meet its product specification requirements, taking into consideration all the high frequency non-idealities of system, circuit, layout, package and board implementation.

Traditionally, designers have followed a step-by-step design process in which each step is isolated from the others by different design environments and databases. The non-ideal high frequency effects of each implementation step on the previous steps are either not considered at all, or are dealt with as a post back-annotation process. Often these effects, because they are not addressed during the design process, require major redesign iterations in order to meet product specifications, thus creating critical and costly delays in getting products to market.

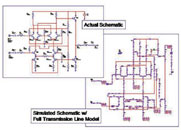

Concurrent Interconnect-driven Design Methodology

Accurate modeling and analysis during the RFIC design process is critical for an efficient, successful product-to-market process. The Analog Office design suite provides the industry's first interconnect-driven/RF aware design methodology, which is built on the Intelligent Net™ (iNet) technology. Similar to timing-driven or wire-driven digital design methodologies, the interconnect-driven methodology focuses on accurate RF interconnect modeling and analysis throughout the entire RFIC design process (see Figure 6 ). This reduces or eliminates design iterations, shortens the design cycle and ensures first-time design success. Existing net constructs are built on a digital-centric data model, while the Analog Office iNet technology is based on an RF-accurate net model with multiple levels of abstraction, ranging from an ideal short-circuit model to a lumped element model, to a distributed RLC model, to a fully distributed transmission line model, or, ultimately, to a full 3D EM model. The example in Figure 7 shows that with iNet technology, all the interconnects in the circuit schematic on the upper left can be automatically extracted and modeled in full distributed transmission lines, as shown in the schematic on the lower right. Thus, detailed parasitic effects at RF can be modeled accurately without the designer having to add explicit transmission line elements to the schematic.

RFIC Process Design Kits

Next-generation EDA solutions can provide powerful custom IC layout capabilities that are tightly integrated with the simulator. However, to take advantage of the integrated simulation and layout capabilities, users must have access to foundry-specific libraries that tie together the electrical and physical representations of active and passive elements. RFIC foundries have been inconsistent in the definition and actual delivery of process design kits (PDK), partially because of the broad variety of methodologies employed by foundry customers, but also as a consequence of process and modeling issues. The integrity of the electrical and physical model data is often a contentious issue between foundry customers, foundries and EDA vendors.

Neither an EDA company nor a foundry can deliver an optimal PDK in isolation. The foundry, while having a better understanding of the process variations and tolerances, does not have the software expertise to fully leverage the EDA platform. On the other hand, the EDA company can develop a library around a process guide. Without access to validation data or the latest process changes, however, the library can quickly become inconsistent or unreliable. AWR has established close partnerships with leading RFIC foundries to deliver validated libraries and to provide validated PDKs that include integrated electrical models, parameterized cell libraries and DRC files for efficient design. These partnerships, initially driven by mutual customers, are providing cost advantages for designers by establishing a validated standard that enables them to focus more effort on the design and less time configuring the software. End users, commercial foundries and EDA vendors can all benefit from the reduced support effort, higher customer satisfaction, and shorter design cycles that result from integrated foundry libraries. AWR is engaged with all the major semiconductor foundries worldwide to develop foundry-specific libraries or design kits targeting SiGe, BiCMOS and RF CMOS processes.

Accurate EM and Circuit Analysis

EM analysis and circuit simulation are clearly complementary technologies for RF and microwave IC design. While circuit simulators are extremely fast, they lack the ability to handle arbitrary structures such as interconnecting vias, airbridges and the parasitic effects introduced by packaging RFICs. On top of the physical challenges, designers are also confronted with inputting accurate discontinuity models and integrated EM analysis into a coherent EDA-based design methodology. The Analog Office design suite has unique EM-based discontinuity models that effectively deliver EM accuracy with the speed of circuit analysis tools. This library of discontinuity models is built around a database of full wave EM simulation data. The models, developed to specifically address the requirements for high frequency communications applications, use EM analysis to provide vastly expanded ranges of validity in addition to improved accuracy. In addition, integrated EM analysis capabilities can display currents and E-field animations for arbitrary multi-layered structures. The Analog Office 2003 solution supports integrated 3-D planar EM simulation with circuit simulation and layout tools, enabling arbitrary structures to be embedded within linear and nonlinear circuit simulations (see Figure 8 ). The Analog Office tool set spans the entire IC design flow, from system level to circuit level and physical design and verification. The unified RF data model enables new levels of interactivity between schematic and layout designs, and maintains the connectivity between the two representations in real time.

Conclusion

The unique challenges presented by the design and production of today's complicated RFICs have hampered the progress of electronic design automation innovation in this area over the past decade. The recent introduction of new EDA platforms that address these challenges in a completely different way has, however, opened the door to future progress in streamlining the RFIC development process. The combination of high quality layout editors with robust connections to simulation provides a basis for rapid product development cycles. Partnerships between foundries and EDA vendors are producing more capable and integrated RFIC PDKs that speed the design process while improving reliability. The future looks much brighter for designers under pressure to produce complicated, innovative designs in short time-to-market cycles.