Product Feature

Monolithic RF Matrix Switches

Peregrine Semiconductor Corp.

San Diego, CA

A new line of fully monolithic 4 x 6 RF matrix switches for cellular infrastructure applications has been introduced. The parts feature low insertion loss, very high port-to-port isolation and serial programmability. These designs represent the state-of-the-art in switching and are the culmination of several years of technology development focused on high level, high performance RF integration.

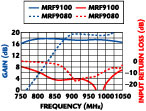

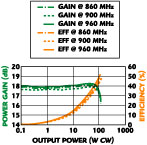

The RF matrix switches are the first in the industry to provide a monolithic 4 x 6 RF switch with a simple programming control interface. The switches are non-blocking, which means any one of the RF input ports can be programmed via the serial peripheral interface (SPI) to connect to any of six output ports simultaneously. They have a typical input 1dB compression point of +31 dBm, and a typical insertion loss of 12 dB over the specified frequency band. The PE4460 switch is designed to support four cellular/GSM inputs, the PE4461 switch four PCS/UMTS inputs, the PE4462 unit three PCS/ UMTS and one cellular/GSM input and the PE4463 switch supports three cellular/GSM and one PCS/UMTS input. A graph of insertion loss and isolation versus frequency, shown in Figure 1 , is indicative of the large bandwidth over which these switches exhibit excellent characteristics. The parts are available in 48-lead 7X7 MLP packages. The programming interface and the actual switching transistors are realized in CMOS, and the resulting current drain of the finished product is less than 1 mA. These devices operate from a single 3 V power supply and offer integrated electrostatic discharge (ESD) protection.

Fig. 1 The PE4460 switch insertion loss and isolation vs. frequency.

At the heart of each design are four six-way Wilkinson type reactive power splitters realized in lumped element fashion with high quality factor inductors on die. The power splitters' role in the design allows for any antenna input to route to any, or all, of the switched outputs. In addition, these matched networks provide the high port-to-port isolation required in a typical radio system. The lumped element devices utilized in the power splitters are photographically defined, which leads to superior element value matching. Consequently, the splitter isolation is > 25 dB between RF modems when they are connected to a common source.

There are four switch products in the initial rollout and they are specifically targeted at the major cellular bands, both domestically and internationally. Table 1 summarizes the salient performance metrics of these new devices.

|

Table 1 | ||||

|

|

PE4460 |

PE4461* |

PE4462 |

PE4463* |

|

Operating |

824 to 924 |

1710 to 2025 |

824 to 9241 |

1710 to 20253 |

|

IIP3 |

50 |

50 |

50 |

50 |

|

P1dB (dBm, typ.) |

31 |

31 |

31 |

31 |

|

Insertion loss |

12 |

13 |

11.71 |

133 |

|

Insertion at 1 GHz (dB) |

45 |

43 |

43 |

43 |

|

Total ICC at 3 V (mA) |

1 |

1 |

1 |

1 |

|

Vcc Range (V) |

2.7 to 3.3 |

2.7 to 3.3 |

2.7 to 3.3 |

2.7 to 3.3 |

|

*Future release | ||||

Application Background

There has been a veritable explosion of cellular telecommunication over the past 20 years. Virtually every metropolitan area in the western world has sufficient infrastructure capacity to carry the full load of mobile phone traffic required by the local user base. Those ubiquitous antenna towers that support call traffic are readily identifiable by virtue of the tri-sectored design they typically employ. Of course, most engineers are aware that this design is optimized to improve channel reuse, which in turn maximizes bandwidth efficiency and operator revenue.

There are numerous system types - for example, GSM and CDMA - and even more numerous architectural variations to these systems that are unique to their respective equipment manufacturers. However, one recurring theme in all of these systems is the need to connect the antenna arrays to the transmitters and receivers of their associated base station hardware.

By way of background, an early industry model suggested that a single traffic channel should statistically have the capacity to carry 50 or more users. Furthermore, a typical cell site should be able to handle on the order of 3000 talkers and, given 60 channels, this should be feasible. Allowing the validity of this argument suggests that any system architecture is viable provided it arrives at sufficient traffic channel capacity. GSM does so by offering 10 traffic channels per RF carrier and a sufficient number of RF carriers to support the appropriate number of channels. In the example cited, six RF modems would suffice. A simplified schematic of a sectored antenna is shown in Figure 2 .

Fig. 2 Typical sectored antenna application.

The system engineer's challenge is to economically route these sectored antennae to the RF modems located inside the base transceiver station (BTS) with the least amount of signal impairment due to path loss and interference. There are several means of accomplishing this function, including non-blocking RF matrix switching. The matrix switch provides a real time capability to dynamically allocate the appropriate number of modems necessary to a given sector based on its actual call volume. In practice, a non-blocking matrix is a combination of RF signal splitters in conjunction with a switch fabric core that allows any input to connect to any or all of the outputs.

A matrix switch operating in the field is very likely comprised of several discrete power splitting networks combined with GaAs single-pole switches arranged in an MxN configuration. While this is a generally acceptable design technique from the standpoint of commercial viability and modularity, it does not represent the acme of economy, current drain or space utilization. Indeed, the designer is even confronted with critical performance problems such as isolation and matching between paths. This design has proven both expensive and technically difficult to implement. An example of a discrete solution is shown in Figure 3 .

Not surprisingly, this type of circuit capability has not been integrated for commercial application to date. One may readily infer that the number of required switches alone represents a fairly significant level of RF complexity. This is just one hurdle that must be overcome. The reactive power signal splitters required must exhibit very high quality factors in order to perform their functions with minimal insertion loss. There is also the non-trivial issue of economically controlling all these switch functions. In this case, economy is measured in dollars and current drain, which also translates to dollars. Finally, and certainly of the utmost importance, is the task of packing all this functionality into a small space while maintaining some very taxing RF performance limits.

Fig. 3 Discrete realization of a 4 x 6 switch function.

Bulk CMOS vs. SOI CMOS

The new matrix switches are made possible by Peregrine's unique RF silicon-on-insulator (SOI) process, UTSi.® The performance versus integration gap has truly been bridged with this proprietary technology. UTSi is an ultra thin layer of silicon on a purely insulating sapphire substrate. The process enables very high performance, fully depleted CMOS transistors in addition to very high quality factor inductors and capacitors. All of these properties are traceable to the sapphire substrate, which is one of the best known insulators.

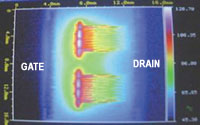

Indeed, the absence of a bulk interface mechanism, which is also traceable to the insulating substrate, is the reason that the UTSi process is inherently capable of manufacturing such high linearity and low loss RF switches. Figures 4 and 5 show simplified cross sectional views and the corresponding small-signal electrical models respectively of bulk CMOS vs. SOI CMOS structures. The dual benefit of bulk effect elimination in conjunction with a low loss tangent non-conducting substrate makes these highly coveted ultra-linear and low loss characteristics possible.

Fig. 4 Bulk CMOS vs. UTSi process comparison.

The electronics industry has in general enjoyed the benefits of technology enhancement and cost reduction for decades. Higher levels of integration, smaller lithographic feature sizes of integrated circuit processing and incredible advances in material science have fueled this continuous improvement in price and performance.

While this level of integration has proven elusive, for a variety of technical and economic considerations, many benefits have evolved as a result of the initiative to get there. The CMOS revolution that followed with the advent of the personal computer is one very compelling example.

Numerous advances of a similar nature have occurred in high performance technologies that are very product-focused toward high integration moderate performance or high performance moderate integration. The simultaneous existence of high performance RF circuit functions and high levels of integration certainly have few widely known examples.

The typical cellular telephone in circulation today is comprised of a highly integrated BiCMOS transceiver chip, or chip set, along with a CMOS baseband signal processing chip and some type of microcontroller. There are numerous support components as well but the fundamental radio functions have literally been reduced to a handful of integrated circuits.

Fig. 5 Small-signal model of a bulk CMOS vs. UTSi device.

The higher parametric performance requirements for cellular infrastructure equipment have resulted in far less integration density to date, as compared to handsets. Not surprisingly, however, the pressure to reduce size and cost and improve power efficiency is becoming a factor for these high performance units as well. In response to this demand the company's design engineering and device technologists have developed unique processes that are specifically optimized to address the need to integrate higher level functionality at the performance levels previously beyond the capability of an IC process. Additional information on the new matrix switches and other related devices may be obtained from the company's Web site at http://www.peregrine-semi.com.

Peregrine Semiconductor Corp., San Diego, CA (858) 455-0660.

Circle No. 301