The need for SWaP (Size, Weight and Power) optimization is stated implicitly or explicitly in almost every new military microwave module RFP. The SWaP acronym began to proliferate after the 2001 Quadrennial Defense Review (QDR) which was published shortly after the September 11th 2001 attacks. This QDR introduced us to the challenges of asymmetric warfare which has been a driving force for greater SWaP reduction. Asymmetric warfare occurs when a large centralized power engages in battle with smaller disparate groups. Addressing asymmetric warfare in addition to conventional warfare means, in addition to monitoring deployments of troops, fleets of ships and tank platoons, that the military has been refining its capabilities to detect and defeat the actions of much smaller groups and even individual hostiles. Dispersed sensing, persistent surveillance, data collection and exploitation, along with precision weapons are just a few of the ways to combat this threat. These systems require more electronics on smaller dispersed platforms, hence the continued focus on reducing SWaP.

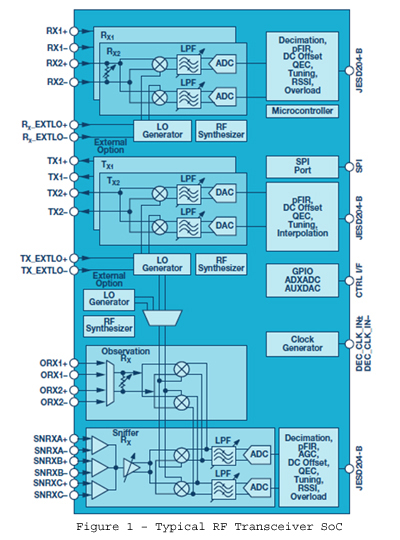

For military microwave module manufacturers, reducing SWaP and cost means looking at all possible levels of integration; at the SoC (System on Chip), at the SiP (System in Package) and at the IMA (Integrated Microwave Assembly)  levels. SoC integration allows for the greatest possible reduction in size and in recurring cost. RF transceivers are just one example of possible on-chip integration. Wideband transceivers offering two transmit and 2 receive channels with integrated LO synthesizers and digital processing functions are now widely available from multiple commercial sources. Supporting many of the RF bands up to 6 GHz, and in the future 12 GHz depending on the supplier, and in packages less than 12mm x 12mm, these provide an unprecedented level of integration. The module level equivalent of these devices could be orders of magnitude larger and more expensive. However, the investment in manpower, time and dollars required to develop a SoC often makes this approach impractical for lower volume applications and in many cases need to support multiple applications to justify the investment.

levels. SoC integration allows for the greatest possible reduction in size and in recurring cost. RF transceivers are just one example of possible on-chip integration. Wideband transceivers offering two transmit and 2 receive channels with integrated LO synthesizers and digital processing functions are now widely available from multiple commercial sources. Supporting many of the RF bands up to 6 GHz, and in the future 12 GHz depending on the supplier, and in packages less than 12mm x 12mm, these provide an unprecedented level of integration. The module level equivalent of these devices could be orders of magnitude larger and more expensive. However, the investment in manpower, time and dollars required to develop a SoC often makes this approach impractical for lower volume applications and in many cases need to support multiple applications to justify the investment.

A lower investment is required to create a SiP that leverage several discrete die. The advantage from the SWaP perspective is that one can place several die in very close proximity to each another. From a cost perspective this approach is well suited to establish high volume automated assembly techniques.

SiP integration comes in several forms, 2D, 2.5D and 3D. The 2D integration approach consists of a planar assembly techniques. These could be wire bonded or flip chip. This approach has the lowest level of NRE required, but would yield the largest of the three SiP approaches.

The 2.5D integration leverages an interposer to connect from die to die. This can allow for greater SWaP reduction because micro-bumps can be used on the interposer allowing for even finer pitch interconnects, stacking and routing in the package.

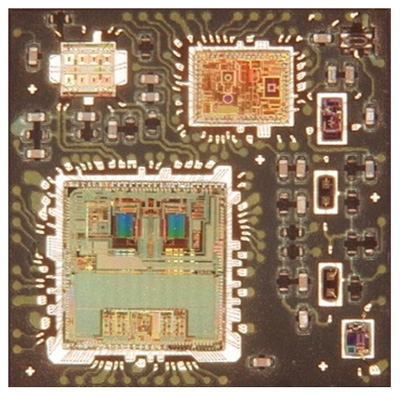

3D integration, which leverages chip-on-chip integration, allows for the greatest SiP SWaP reduction. In 3D assemblies, die are designed specifically to be stacked. This approach yields the smallest of SiP footprints by using specialized high volume assembly equipment. Below is an example of a 2D wirebonded SiP that leverages waveguide launches to ensure optimal performance up to 86 GHz.

Figure 2 – RF radio SiP.

Like SiPs, IMA integration can take many forms. Classically, modules or hybrids are defined as containing heterogeneous semiconductors in a connectorized housing. IMAs also include rack mount chassis, card level solutions and multi-module sub-assemblies, to name a few. Military microwave modules designers have been addressing SWaP issues long before this acronym made its way into our vocabulary. Form factors are often well defined and designers are given the choice of adding more functionality into the existing footprint or giving up volume so additional functionality can be added elsewhere. IMA’s continue to offer SWaP advancements, but not to the extent of the aforementioned chip level integration.

Table 1: Comparison of Integration Techniques

|

Level of Integration |

Size Reduction Potential |

Development Time & NRE Costs |

Production Costs |

Comments |

|

SoC |

Excellent |

Highest |

Lowest |

Custom MMICs required |

|

3D SiP |

Excellent |

High |

Moderate |

Custom MMICs required |

|

2.5D SiP |

Very Good |

Moderate |

Moderate |

Requires Interposer Design |

|

2D SiP |

Very Good |

Low |

Low |

Planar approach |

|

IMA |

Good |

Low |

High |

Connectorized Housings/PWA configurations |

Table 1 summarizes the potential SWaP reduction opportunity, development time, costs for NRE and Production. Each of the parameters are highly dependent on the complexity of the functionality being integrated and key performance requirements. Program requirements, milestones and levels of investment often drive integration decisions. Module companies that understand multi-market needs can work closely with system integrators to identify common functionality and choose the right level of integration or right combination of levels of integration and initiate advanced development activities. This can mitigate schedule risk associated with the greatest potential SWaP optimization, cost and performance of future system.