Microfabrication of glass micro-devices and circuits has been historically difficult at the part level, let alone in a high volume manufacturing (HVM) environment, due to low throughput, limited precision and accuracy, and reduced reliability, as well as limited process and design capabilities. A new photo-definable glass ceramic material has been developed that is processed in a three-step batch process enabling an HVM solution for glass microfabrication. Since the technology is based on a lithographic process, many design and process capabilities not typically associated with glass microfabrication are now possible, such as through glass vias (TGV) for I/Os, complex inductor line structures, high Q-factor architectures, and antenna air bridges on a single electrical substrate. The material’s fine surface finish also enables an MCM capability with fully integrated thin film passive components such as resistors, capacitors and inductors.

Glass materials have many ideal properties for RF and microwave electronic packaging, including high strength, smooth surfaces for efficient signal distribution and excellent electrical characteristics; however, traditional glass manufacturing techniques (e.g., deep reactive-ion etching [DRIE], sand blasting and laser processing) suffer from low throughput, low yield, limited precision and accuracy and limited design capabilities. This prevents even the most basic packaging features like through glass vias (TGV) from being used in high volume applications.

For these reasons, most RF and microwave electronic packages are produced using materials such as laminates and solid ceramics. These are unsuitable for many applications, however, because circuit integration is constrained by flatness and warpage limitations; the inability to produce large scale through-substrate vias results in long interconnection paths between

I/Os; high surface roughness prevents the use of small metal line widths; and many of these materials, such as alumina, are expensive to use and process.

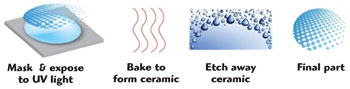

Figure 1 APEX® Glass processing steps.

With the newly developed APEX® Glass process, features such as TGVs, trenches and embedded microstructures (e.g., inductors and antennas) may be simultaneously microfabricated using a precise, rapid and cost effective batch manufacturing process. The ability to produce electronic packages that integrate these types of structures enables many types of packaging architectures across military, communications and portable consumer electronics industries.

Processing Approach

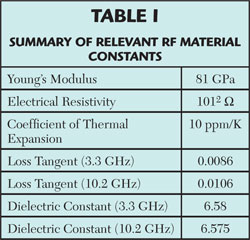

APEX Glass is a photosensitive glass-ceramic material capable of existing in both an amorphous glass state and a crystallized ceramic state. Leveraging the differences between these states allows designers to produce RF and microwave electronic structures not commonly associated with glass processing. Table 1 lists several of its material characteristics.

The material is batch processed in three steps (see Figure 1). First, a chrome-on-quartz mask is placed directly onto the glass wafer, without photoresist, and exposed to 310 nm light. During this step, photo-activators in the glass become chemically reduced.

In the second step, the wafer is baked. The temperature is initially raised to a level that allows the photo-activators to migrate together forming nano-clusters and is then ramped up to a second level to facilitate coalescence of ceramic-forming ions around the nano-clusters. During this phase of the baking process, any previously exposed regions are converted into a ceramic state, where increased levels of exposure lead to more complete ceramic formation.

In the final step, the wafer is etched in a dilute hydrofluoric acid solution (e.g., 10 percent), etching the ceramic state 60 times more preferentially than the glass state. In this manner, a wide variety of features, such as posts, wells, TGVs, trenches, blind vias and air bridges may be produced. The desired structure depth, or the amount of undercutting, is controlled by etch concentration, processing duration, bath temperature and etching direction.

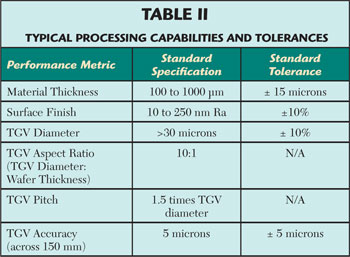

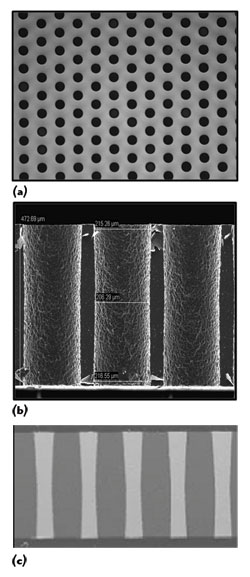

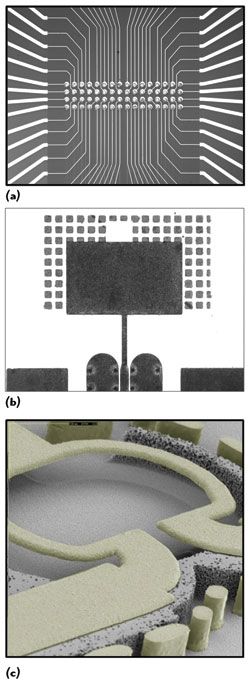

The lithography-based patterning process produces accurate and precise manufacturing features (see Table 2). For example, TGVs as small as 30 microns in diameter at pitches as small as 1.5 times the TGV diameter may be produced with micron-scale features and positional accuracy on the production substrate. Figure 2a shows an array of 60-micron diameter TGVs at a pitch of 150-microns. The differences between glass and ceramic etch selectivities enable the production of anisotropic etch profiles greater than 10:1 (TGV diameter: material thickness) as shown in Figure 2b. These anisotropic profiles allow for the efficient packing of electronic I/Os enabling densely packed TGV array (e.g., wide I/O) architectures. Figure 2c shows a cross-section of a fully copper plated TGV array.

Figure 2 TGV array (a), 200-micron diameter TGVs demonstrating anisotropic etch (b), cross-section of 75-micron diameter, 800-micron thick copper plated (lighter color) TGVs (c).

Figure 3 Redistribution layer (a), 15-micron thick electroplated copper features (b), millimeter wave circuit with 35-micron air bridges (c).

Similar to other commercially available glass materials, its surface finish facilitates a number of surface modifications such as thin and thick film metallizations. A surface roughness of less than 40 nm is common for most RF and microwave applications and enables the production of sub-10 micron wide line widths for redistribution. Figure 3a, for example, shows a redistribution layer of 10-micron lines on 20-micron pitch connecting to 50-micron TGVs. Furthermore, the fine surface finish of the material enables MCM capability with fully integrated thin film passive components such as resistors, capacitors and inductors. Figure 3b shows that thick layers (>10 microns) of copper and other metals may be electroplated onto the surface. Figure 3c shows a millimeter wave electronic circuit with 35-micron critical dimensions, demonstrating that the adhesion between electroplated metal and the glass surface is strong enough to withstand additional downstream processing such as post-electroplating wet etching to create air bridge architectures.

Advanced RF Designs

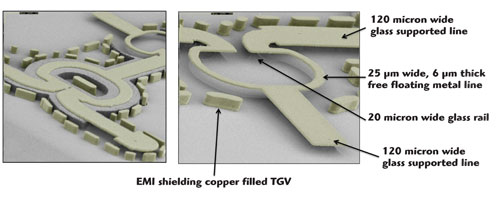

The process enables complex RF electronics not typically associated with glass materials. In many applications, high Q-factor architectures are necessary for efficient, low power communications. For these applications, it offers several degrees-of-freedom in design and production. Figure 4 shows a high Q-factor millimeter-wave structure that consists of 120-micron wide, 6-micron thick, copper lines resting on 20-micron wide glass rails, with 25-micron wide copper lines free floating 100 microns above the underlying glass material. The entire circuit is surrounded by solid copper EMI features, grounded on the backside.

The package demonstrates three key design features:

Glass rails support surface metallization by providing rigidity for the metal lines to rest on while removing the majority of underlying glass material, enabling the metal lines to be surrounded by air. Support rails may be produced in a number of geometries, however, the central line architecture is the most common. Rails ranging from 10 to 100 microns have been demonstrated.

Air bridges of surface metal lines are used in a number of RF architectures. Air bridges of metal lines ranging from 10 to 1000 microns have been demonstrated. Air bridges may exist as undercut surface metal lines with the glass 150-microns below the metal line, or they may consist of free-floating metal lines spanning millimeters of space where no glass exist below the metallization.

Figure 4 High Q-factor millimeter-wave circuit surrounded by solid copper EMI features grounded on the backside.

In-Chip EMI shielding structures, such as the through glass copper pillars may be built into almost any application to minimize unwanted RF radiation. EMI features are produced in a similar manner as TGVs for I/Os, however, whereas I/Os are typically round and used to connect the top of the substrate to the bottom of the substrate, EMI features may take on a variety of shapes and sizes, as shown in Figure 3c, and are all grounded together on the bottom of the substrate. In Figure 4, 30-micron wide, 120-micron long (4:1, length: width ratio), solid copper EMI features are shown. EMI features with aspect ratios up to 8:1 may be produced in almost any RF circuit.

Process Flow

The example shown in Figure 4 is manufactured using the following standard wafer-level semiconductor process.

- Exposure using a 500 W OAI flood exposure tool with 300 to 320 nm narrow pass mirrors is performed at a power density of 20 mW/cm2. A chrome-on-quartz lithography mask is used during the contact exposure, with no photoresist. Exposure of the glass includes all features to be etched, including TGVs for I/Os, TGVs for EMI shielding and regions to etch for undercutting of metal lines.

- The wafer is baked at 500°C for 75 minutes at a ramp rate of 6°C per minute and then at 575°C for 75 minutes at a ramp rate of 3°C per minute, converting all of the previously exposed regions to ceramic.

- A chrome hard mask is applied to all ceramic features on both sides of the wafer except I/O and EMI shielding TGVs. All TGVs are double sided etched in 10 percent HF acid.

- All TGVs for I/Os and EMI shielding are copper filled using standard electrolytic copper filling techniques. Copper plating overburden is mechanically polished using standard techniques.

- Surface metal structures are patterned using standard photolithography techniques. Briefly, a thin seed layer of copper is blanket deposited onto the surface of the wafer. Photoresist is applied to the wafer and patterned to the exact locations to represent the surface metal. Open metal features are electroplated with copper to a final thickness of 6-microns. Next, the photoresist is stripped and the unplated seed layer chemically removed exposing the underlying glass or ceramic material.

- The wafer is placed into a 5 percent HF acid and etched for approximately 15 minutes to form glass rails and air bridges, etching the ceramic at approximately 10-microns per minute. The desired depth of the etched relief is controlled by controlling the total etch time.

Conclusion

APEX Glass is a flexible and cost effective substrate for a number of RF and microwave applications by providing a material for batch manufacturing of wafer-level components with simple processing and low production costs. This new manufacturing approach enables fabrication of very complex RF electronics not typically associated with glass processes. These devices may include TGVs, air bridges, EMI shielding and glass support rails with small dimensions.